[llvm] [RFC][MC] Cache MCRegAliasIterator (PR #93510)

Pierre van Houtryve via llvm-commits

llvm-commits at lists.llvm.org

Mon Jun 3 05:46:07 PDT 2024

================

@@ -726,60 +730,122 @@ class MCRegUnitRootIterator {

/// MCRegAliasIterator enumerates all registers aliasing Reg. If IncludeSelf is

/// set, Reg itself is included in the list. This iterator does not guarantee

/// any ordering or that entries are unique.

+///

+/// This iterator can work in two modes: cached and uncached.

----------------

Pierre-vh wrote:

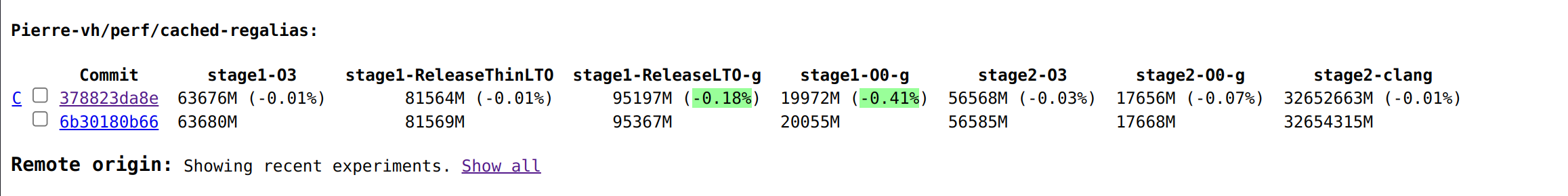

I did that first because I assumed we'd like a killswitch of some kind for targets where the cache doesn't help, but if I read the compile time tracker diff correctly, it seems to be a universal win so I'll revisit it and split up the implementation

https://github.com/llvm/llvm-project/pull/93510

More information about the llvm-commits

mailing list