[clang] [InstCombine] Refactor matchFunnelShift to allow more pattern (NFC) (PR #68474)

via cfe-commits

cfe-commits at lists.llvm.org

Sat Oct 14 18:18:20 PDT 2023

================

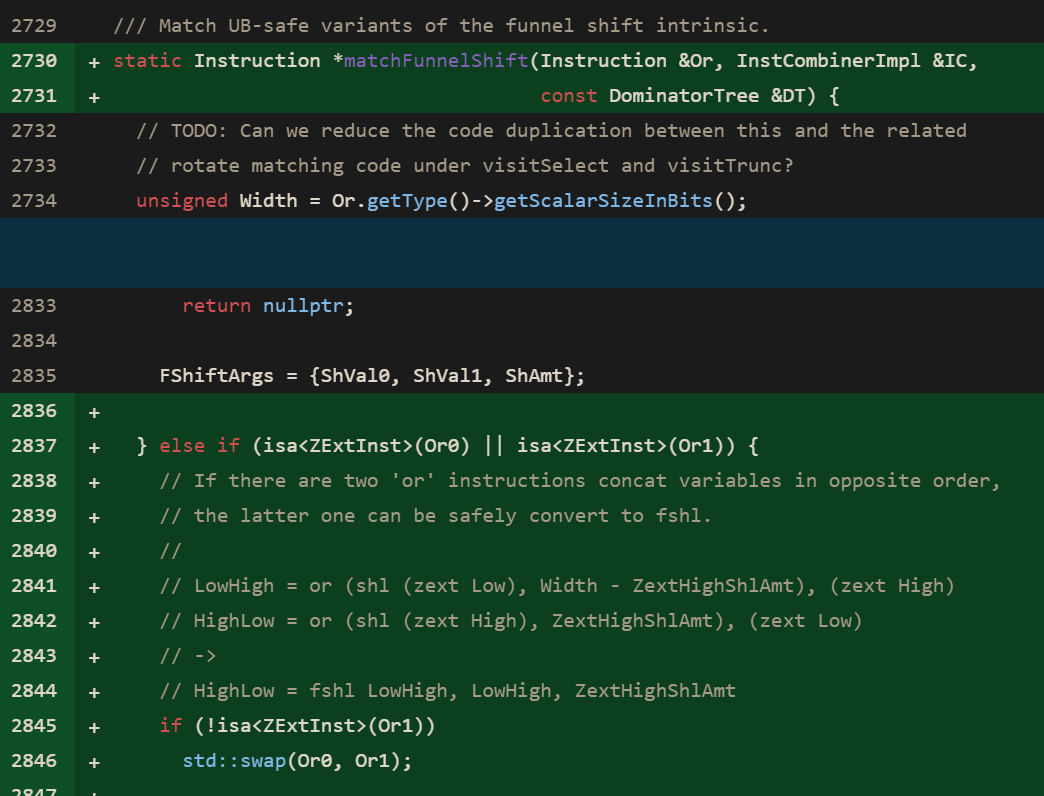

@@ -2732,100 +2732,114 @@ static Instruction *matchFunnelShift(Instruction &Or, InstCombinerImpl &IC) {

// rotate matching code under visitSelect and visitTrunc?

unsigned Width = Or.getType()->getScalarSizeInBits();

- // First, find an or'd pair of opposite shifts:

- // or (lshr ShVal0, ShAmt0), (shl ShVal1, ShAmt1)

- BinaryOperator *Or0, *Or1;

- if (!match(Or.getOperand(0), m_BinOp(Or0)) ||

- !match(Or.getOperand(1), m_BinOp(Or1)))

- return nullptr;

-

- Value *ShVal0, *ShVal1, *ShAmt0, *ShAmt1;

- if (!match(Or0, m_OneUse(m_LogicalShift(m_Value(ShVal0), m_Value(ShAmt0)))) ||

- !match(Or1, m_OneUse(m_LogicalShift(m_Value(ShVal1), m_Value(ShAmt1)))) ||

- Or0->getOpcode() == Or1->getOpcode())

+ Instruction *Or0, *Or1;

+ if (!match(Or.getOperand(0), m_Instruction(Or0)) ||

+ !match(Or.getOperand(1), m_Instruction(Or1)))

return nullptr;

- // Canonicalize to or(shl(ShVal0, ShAmt0), lshr(ShVal1, ShAmt1)).

- if (Or0->getOpcode() == BinaryOperator::LShr) {

- std::swap(Or0, Or1);

- std::swap(ShVal0, ShVal1);

- std::swap(ShAmt0, ShAmt1);

- }

- assert(Or0->getOpcode() == BinaryOperator::Shl &&

- Or1->getOpcode() == BinaryOperator::LShr &&

- "Illegal or(shift,shift) pair");

-

- // Match the shift amount operands for a funnel shift pattern. This always

- // matches a subtraction on the R operand.

- auto matchShiftAmount = [&](Value *L, Value *R, unsigned Width) -> Value * {

- // Check for constant shift amounts that sum to the bitwidth.

- const APInt *LI, *RI;

- if (match(L, m_APIntAllowUndef(LI)) && match(R, m_APIntAllowUndef(RI)))

- if (LI->ult(Width) && RI->ult(Width) && (*LI + *RI) == Width)

- return ConstantInt::get(L->getType(), *LI);

-

- Constant *LC, *RC;

- if (match(L, m_Constant(LC)) && match(R, m_Constant(RC)) &&

- match(L, m_SpecificInt_ICMP(ICmpInst::ICMP_ULT, APInt(Width, Width))) &&

- match(R, m_SpecificInt_ICMP(ICmpInst::ICMP_ULT, APInt(Width, Width))) &&

- match(ConstantExpr::getAdd(LC, RC), m_SpecificIntAllowUndef(Width)))

- return ConstantExpr::mergeUndefsWith(LC, RC);

-

- // (shl ShVal, X) | (lshr ShVal, (Width - x)) iff X < Width.

- // We limit this to X < Width in case the backend re-expands the intrinsic,

- // and has to reintroduce a shift modulo operation (InstCombine might remove

- // it after this fold). This still doesn't guarantee that the final codegen

- // will match this original pattern.

- if (match(R, m_OneUse(m_Sub(m_SpecificInt(Width), m_Specific(L))))) {

- KnownBits KnownL = IC.computeKnownBits(L, /*Depth*/ 0, &Or);

- return KnownL.getMaxValue().ult(Width) ? L : nullptr;

- }

+ bool IsFshl = true; // Sub on LSHR.

+ SmallVector<Value *, 3> FShiftArgs;

- // For non-constant cases, the following patterns currently only work for

- // rotation patterns.

- // TODO: Add general funnel-shift compatible patterns.

- if (ShVal0 != ShVal1)

+ // First, find an or'd pair of opposite shifts:

+ // or (lshr ShVal0, ShAmt0), (shl ShVal1, ShAmt1)

+ if (isa<BinaryOperator>(Or0) && isa<BinaryOperator>(Or1)) {

----------------

HaohaiWen wrote:

> This code seems new? Not that its wrong or anything.

I added this if statement in this patch.

It can be early returned in this patch, but I'd like to add another else if on https://github.com/llvm/llvm-project/pull/68502/commits/5b3b1bbb5b263bc5711adde031d85b1461ccbab6. If I removed this if statement, then I need to add the if back and indent the code in the if statement on https://github.com/llvm/llvm-project/pull/68502. This make the diff not clear.

https://github.com/llvm/llvm-project/pull/68474

More information about the cfe-commits

mailing list