[llvm] [clang] X86::LAR X86::LSL add_implicate eflags (PR #80993)

via llvm-commits

llvm-commits at lists.llvm.org

Wed Feb 7 06:23:19 PST 2024

https://github.com/Qfrost911 created https://github.com/llvm/llvm-project/pull/80993

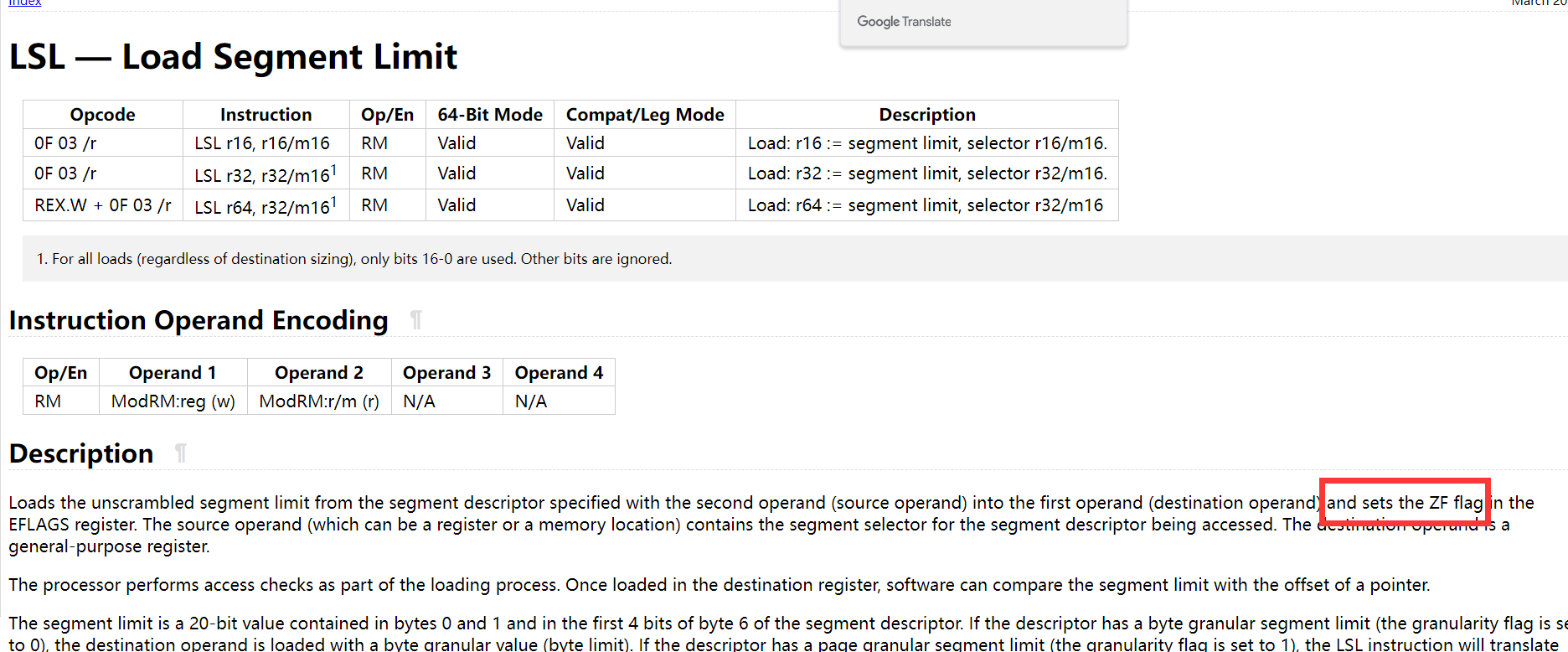

[@xia0ji233](https://github.com/xia0ji233) and I found that X86::LAR and X86::lSR implicit use eflags register. However, it was not been defined in LLVM, which means we will get wrong alive-result if we use these two instructions.

>From b3133c1c8f32e8509885c1f0bf7e88b163f0e643 Mon Sep 17 00:00:00 2001

From: Qfrost <root at qfrost.com>

Date: Wed, 7 Feb 2024 22:13:10 +0800

Subject: [PATCH] X86::LAR X86::LSL add_implicate eflags

---

llvm/lib/Target/X86/X86InstrSystem.td | 2 ++

1 file changed, 2 insertions(+)

diff --git a/llvm/lib/Target/X86/X86InstrSystem.td b/llvm/lib/Target/X86/X86InstrSystem.td

index a7899a2492b882..24a334d38f9261 100644

--- a/llvm/lib/Target/X86/X86InstrSystem.td

+++ b/llvm/lib/Target/X86/X86InstrSystem.td

@@ -213,6 +213,7 @@ def MOV16sm : I<0x8E, MRMSrcMem, (outs SEGMENT_REG:$dst), (ins i16mem:$src),

let SchedRW = [WriteSystem] in {

def SWAPGS : I<0x01, MRM_F8, (outs), (ins), "swapgs", []>, TB;

+let Defs = [EFLAGS] in {

let mayLoad = 1 in

def LAR16rm : I<0x02, MRMSrcMem, (outs GR16:$dst), (ins i16mem:$src),

"lar{w}\t{$src, $dst|$dst, $src}", []>, TB,

@@ -253,6 +254,7 @@ def LSL64rm : RI<0x03, MRMSrcMem, (outs GR64:$dst), (ins i16mem:$src),

"lsl{q}\t{$src, $dst|$dst, $src}", []>, TB;

def LSL64rr : RI<0x03, MRMSrcReg, (outs GR64:$dst), (ins GR16orGR32orGR64:$src),

"lsl{q}\t{$src, $dst|$dst, $src}", []>, TB;

+}

def INVLPG : I<0x01, MRM7m, (outs), (ins i8mem:$addr), "invlpg\t$addr", []>, TB;

More information about the llvm-commits

mailing list