[all-commits] [llvm/llvm-project] 5f6640: [OpenMP52][LIBOMPTARGET] Do not throw error in omp...

John Demme via All-commits

all-commits at lists.llvm.org

Thu Feb 8 09:23:51 PST 2024

Branch: refs/heads/users/teqdruid/mlir/python-liveobjects

Home: https://github.com/llvm/llvm-project

Commit: 5f6640e268b5e6ead22983ba9e2074e3bbf0612b

https://github.com/llvm/llvm-project/commit/5f6640e268b5e6ead22983ba9e2074e3bbf0612b

Author: Saiyedul Islam <Saiyedul.Islam at amd.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M openmp/libomptarget/src/OpenMP/API.cpp

Log Message:

-----------

[OpenMP52][LIBOMPTARGET] Do not throw error in omp_get_mapped_ptr for the host (#80038)

OpenMP spec 5.2 specifies return value to be the host ptr

in case of device_num being same as omp_get_initial_device().

Commit: 285bc69846e76af805cd106ea3ea538a12f5c9b6

https://github.com/llvm/llvm-project/commit/285bc69846e76af805cd106ea3ea538a12f5c9b6

Author: Alexey Bataev <a.bataev at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Transforms/Vectorize/SLPVectorizer.cpp

A llvm/test/Transforms/SLPVectorizer/SystemZ/minbitwidth-trunc.ll

Log Message:

-----------

[SLP]Fix PR80027: Fix costs processing for minbitwidth types.

Need to switch the types, the destination is first in getCastInstrCost

function.

Commit: 3477bcf4b94395e2c0ed77a139e54240cfe4f27d

https://github.com/llvm/llvm-project/commit/3477bcf4b94395e2c0ed77a139e54240cfe4f27d

Author: Guray Ozen <guray.ozen at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M mlir/include/mlir/Dialect/NVGPU/IR/NVGPU.td

A mlir/test/Dialect/NVGPU/canonicalization.mlir

Log Message:

-----------

[mlir][nvgpu] Mark TMA descriptor as MemWriteAt in `tma.async.store` (#79427)

Commit: 201eb2b5775cf193c97c60a5eb790003a1e6bedb

https://github.com/llvm/llvm-project/commit/201eb2b5775cf193c97c60a5eb790003a1e6bedb

Author: Aaron Ballman <aaron at aaronballman.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/docs/ReleaseNotes.rst

M clang/lib/AST/ExprConstant.cpp

M clang/lib/CodeGen/CGExpr.cpp

M clang/lib/Sema/SemaChecking.cpp

M clang/lib/Sema/SemaOverload.cpp

R clang/test/AST/ast-dump-static-operators.cpp

M clang/test/CodeGenCXX/cxx2b-static-call-operator.cpp

M clang/test/CodeGenCXX/cxx2b-static-subscript-operator.cpp

R clang/test/SemaCXX/cxx2b-static-operator.cpp

Log Message:

-----------

Revert "[clang] static operators should evaluate object argument (#68485)"

This reverts commit 30155fc0ef4fbdce2d79434aaae8d58b2fabb20a.

It seems to have broken some tests in clangd:

http://45.33.8.238/linux/129484/step_9.txt

Commit: e1ddc3331210957cec2569cef79021fa69363ab1

https://github.com/llvm/llvm-project/commit/e1ddc3331210957cec2569cef79021fa69363ab1

Author: Louis Dionne <ldionne.2 at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libcxx/include/__thread/support.h

M libcxx/include/__thread/support/c11.h

M libcxx/include/__thread/support/pthread.h

M libcxx/include/__thread/support/windows.h

Log Message:

-----------

[libc++] Move __libcpp_timespec_t into namespace std (#80004)

It was previously defined outside of namespace std for apparently no

good reason.

Commit: 97d72839301e6fd005fb258322b96bd46086daa1

https://github.com/llvm/llvm-project/commit/97d72839301e6fd005fb258322b96bd46086daa1

Author: Cyndy Ishida <cyndy_ishida at apple.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/include/llvm/TextAPI/Symbol.h

Log Message:

-----------

[TextAPI] Fix -Wdocumentation error, NFC

Commit: f2a78e68eee53646327f71c475c7f18a28b7f576

https://github.com/llvm/llvm-project/commit/f2a78e68eee53646327f71c475c7f18a28b7f576

Author: Joseph Huber <huberjn at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/docs/HIPSupport.rst

M clang/lib/Basic/Targets/AMDGPU.cpp

M clang/test/CodeGenOpenCL/builtins-amdgcn-wave64.cl

M clang/test/Preprocessor/predefined-arch-macros.c

Log Message:

-----------

[AMDGPU] Do not emit arch dependent macros with unspecified cpu (#80035)

Summary:

Currently, the AMDGPU toolchain accepts not passing `-mcpu` as a means

to create a sort of "generic" IR. The resulting IR will not contain any

target dependent attributes and can then be inserted into another

program via `-mlink-builtin-bitcode` to inherit its attributes.

However, there are a handful of macros that can leak incorrect

information when compiling for an unspecified architecture. Currently,

things like the wavefront size will default to 64, which is actually

variable. We should not expose these macros unless it is known.

Commit: 5470ea4e36d47ed09595517854f0fa07ca91e16f

https://github.com/llvm/llvm-project/commit/5470ea4e36d47ed09595517854f0fa07ca91e16f

Author: Joseph Huber <huberjn at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libc/src/__support/GPU/amdgpu/utils.h

M libc/src/__support/GPU/generic/utils.h

M libc/src/__support/GPU/nvptx/utils.h

M libc/src/__support/RPC/rpc.h

M libc/utils/gpu/server/rpc_server.h

Log Message:

-----------

[libc] Change the starting port index to use the SMID (#79200)

Summary:

The RPC interface uses several ports to provide parallel access. Right

now we begin the search at the beginning, which heavily contests the

early ports. Using the SMID allows us to stagger the starting index

based off of the cluster identifier that is executing the current warp.

Multiple warps can share an SM, but it will guaruntee that the

contention for the low indices is lower.

This also increases the maximum port size to around 4096, this is

because 512 isn't enough to cover the full hardare parallelism needed to

guarantee this doesdn't deadlock.

Commit: 626fe71fa5ed79cbd41b7b29582560d7adb1220e

https://github.com/llvm/llvm-project/commit/626fe71fa5ed79cbd41b7b29582560d7adb1220e

Author: Joseph Huber <huberjn at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/test/Preprocessor/predefined-arch-macros.c

Log Message:

-----------

[Clang] Fix test failing on systems without ROCm installed

Summary:

Forgot to specify `-nogpulib` which makes this test look for ROCm.

Commit: 85a847fd1d639a0e7d5319b17e994ea157be6046

https://github.com/llvm/llvm-project/commit/85a847fd1d639a0e7d5319b17e994ea157be6046

Author: Konstantin Varlamov <varconsteq at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libcxx/test/libcxx/atomics/atomics.align/align.pass.cpp

M libcxx/test/libcxx/atomics/atomics.types.generic/atomics.types.float/lockfree.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/assign.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/compare_exchange_strong.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/compare_exchange_weak.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/ctor.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/exchange.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/fetch_add.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/fetch_sub.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/load.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/lockfree.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/notify_all.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/notify_one.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.float.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.minus_equals.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.plus_equals.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/store.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/wait.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_compare_exchange_strong.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_compare_exchange_strong_explicit.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_compare_exchange_weak.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_compare_exchange_weak_explicit.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_exchange.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_exchange_explicit.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_init.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_is_lock_free.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_load.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_load_explicit.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_store.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.req/atomic_store_explicit.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.wait/atomic_notify_all.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.wait/atomic_notify_one.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.wait/atomic_wait.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.wait/atomic_wait_explicit.pass.cpp

M libcxx/test/support/atomic_helpers.h

M libcxx/utils/libcxx/test/features.py

Log Message:

-----------

[libc++] Simplify features for detecting atomics' support. (#75553)

`non-lockfree-atomics` is very similar to `has-64-bit-atomics`; to

simplify, we can have uniform features for atomic types of

increasing sizes (`has-128-bit-atomics`, `has-256-bit-atomics`, etc.).

`is-lockfree-runtime-function` feature was a workaround for the partial

support for large atomic types on older versions of macOS (see

https://reviews.llvm.org/D91911). While we still support macOS 10.14,

conceptually it's simpler to check for support for all the atomic

functionality inside the `has-*-atomics` features, and the workaround is

no longer worth the maintenance cost.

Commit: 6fecfbc7b62f54bd633e83c22630d7c2a3e5741e

https://github.com/llvm/llvm-project/commit/6fecfbc7b62f54bd633e83c22630d7c2a3e5741e

Author: Joseph Huber <huberjn at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/lib/Basic/Targets/AMDGPU.cpp

Log Message:

-----------

[AMDGPU] Correctly exclude the HIP host from arch macros

Summary:

This logic was wrong and accidentally appling to OpenCL.

Commit: 733b86d3ff8087f1e267c23eb315bb16e3c6c953

https://github.com/llvm/llvm-project/commit/733b86d3ff8087f1e267c23eb315bb16e3c6c953

Author: Chelsea Cassanova <chelsea_cassanova at apple.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M lldb/include/lldb/Core/DebuggerEvents.h

M lldb/include/lldb/Core/Progress.h

M lldb/source/Core/DebuggerEvents.cpp

M lldb/source/Core/Progress.cpp

Log Message:

-----------

[lldb][progress] Correctly check total for deterministic progress (#79912)

The `total` parameter for the constructor for Progress was changed to a

std::optional in https://github.com/llvm/llvm-project/pull/77547. It was originally set to 1 to indicate non-determinisitic progress, but this commit changes this. First, `UINT64_MAX` will again be used for non-deterministic progress, and `Progress` now has a static variable set to this value so that we can use this instead of a magic number.

The member variable `m_total` could be changed to a std::optional as

well, but this means that the `ProgressEventData::GetTotal()` (which is

used for the public API) would

either need to return a std::optional value or it would return some

specific integer to represent non-deterministic progress if `m_total` is

std::nullopt.

Commit: 1d3300d5027c95c84b335f6adfca7e49cae45bb2

https://github.com/llvm/llvm-project/commit/1d3300d5027c95c84b335f6adfca7e49cae45bb2

Author: Peiming Liu <36770114+PeimingLiu at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M mlir/lib/Dialect/SparseTensor/Transforms/Utils/SparseTensorLevel.cpp

M mlir/lib/Dialect/SparseTensor/Transforms/Utils/SparseTensorLevel.h

Log Message:

-----------

[mlir][sparse] use shared value storage between wrapped iterator and the wrapper. (#80046)

Commit: 235f1e74fe240e414718c64d05bafc01d34c32cb

https://github.com/llvm/llvm-project/commit/235f1e74fe240e414718c64d05bafc01d34c32cb

Author: Jinsong Ji <jinsong.ji at intel.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Basic/Builtins.td

Log Message:

-----------

[Clang] Fix typo in __fprintf_chk Prototype (#80012)

An extra int was copied.

Commit: 30b9140c148923e31a6dbcb2202ef3908481bb29

https://github.com/llvm/llvm-project/commit/30b9140c148923e31a6dbcb2202ef3908481bb29

Author: Craig Topper <craig.topper at sifive.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/test/MC/RISCV/rv32zbb-only-valid.s

M llvm/test/MC/RISCV/rv32zbb-valid.s

M llvm/test/MC/RISCV/rv64zbb-valid.s

M llvm/test/MC/RISCV/rv64zbkb-valid.s

Log Message:

-----------

[RISCV] Minor cleanup to rori MC layer testing. NFC

rv32zbb-valid.s tests rv64 and rv32. rv32zbb-only-valid.s only tests rv32.

The rori tests in rv32zbb-only-valid.s produce the same result for rv32 and

rv64 so its better to test them in rv32zbb-valid.s.

Remove a now redundant test case from rv64zbb-valid.s.

Add a missing rori test with imm >= 32 to rv64zbkb-valid.s.

Commit: 6a21e00e397648141ed36aae4bd958efa09908f3

https://github.com/llvm/llvm-project/commit/6a21e00e397648141ed36aae4bd958efa09908f3

Author: Shilei Tian <i at tianshilei.me>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/AMDGPU/AsmParser/AMDGPUAsmParser.cpp

A llvm/test/MC/AMDGPU/writelane_m0.s

A llvm/test/MachineVerifier/writelane_m0.mir

Log Message:

-----------

[AMDGPU][AsmParser] Allow `v_writelane_b32` to use SGPR and M0 as source operands at the same time (#78827)

Currently the asm parser takes `v_writelane_b32 v1, s13, m0` as illegal

instruction for pre-gfx11 because it uses two constant buses while the

hardware

can only allow one. However, based on the comment of

`AMDGPUInstructionSelector::selectWritelane`,

it is allowed to have M0 as lane selector and a SGPR used as SRC0

because the

lane selector doesn't count as a use of constant bus. In fact, codegen

can already

generate this form, but this inconsistency is not exposed because the

validation

of constant bus limitation only happens when paring an assembly but we

don't have

a test case when both SGPR and M0 used as source operands for the

instruction.

Commit: d8b61d716899736c7f0444d1b18b8e1a536c3472

https://github.com/llvm/llvm-project/commit/d8b61d716899736c7f0444d1b18b8e1a536c3472

Author: Aiden Grossman <agrossman154 at yahoo.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/docs/CommandGuide/llvm-exegesis.rst

A llvm/test/tools/llvm-exegesis/X86/latency/middle-half.s

M llvm/tools/llvm-exegesis/lib/BenchmarkResult.h

M llvm/tools/llvm-exegesis/lib/CMakeLists.txt

A llvm/tools/llvm-exegesis/lib/ResultAggregator.cpp

A llvm/tools/llvm-exegesis/lib/ResultAggregator.h

M llvm/tools/llvm-exegesis/lib/SnippetRepetitor.cpp

M llvm/tools/llvm-exegesis/llvm-exegesis.cpp

M llvm/unittests/tools/llvm-exegesis/CMakeLists.txt

A llvm/unittests/tools/llvm-exegesis/ResultAggregatorTest.cpp

Log Message:

-----------

[llvm-exegesis] Add middle half repetition mode (#77020)

This patch adds two new repetition modes to llvm-exegesis, particularly

loop and duplicate repetition modes of what I am terming the middle half

repetition mode. The middle half repetition mode essentially runs each

measurement twice, one with twice the number of iterations of the other.

These two measurements are then agregated by taking their difference.

This subtracts away any setup/overhead that is unrelated to the code in

the snippet, providing more accurate results.

Using this mode on a couple toy examples, I am able to get exact

(integer) throughput values on all of them in contrast to the default

duplicate/loop repetition modes which show a little bit of noise on the

snippet value.

Commit: 58e8c072aa4ebb11dfab13ed00fa8d61e408516c

https://github.com/llvm/llvm-project/commit/58e8c072aa4ebb11dfab13ed00fa8d61e408516c

Author: Shilei Tian <i at tianshilei.me>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/test/MachineVerifier/writelane_m0.mir

Log Message:

-----------

[FIX] Require AMDGPU target in test case `llvm/test/MachineVerifier/writelane_m0.mir`

Commit: 0dd0cbd324ad13dd7b91edf69a2ca66a6a208c80

https://github.com/llvm/llvm-project/commit/0dd0cbd324ad13dd7b91edf69a2ca66a6a208c80

Author: erichkeane <ekeane at nvidia.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Basic/OpenACCKinds.h

M clang/lib/Parse/ParseOpenACC.cpp

A clang/test/ParserOpenACC/parse-wait-clause.c

Log Message:

-----------

[OpenACC] Implement 'wait' clause parsing.

The 'wait' clause is parsed the same way as the 'wait' construct, so

this jsut differs to that function.

Commit: 66ef6900f9f3aa4fab9f6e36af04f775948cdf9d

https://github.com/llvm/llvm-project/commit/66ef6900f9f3aa4fab9f6e36af04f775948cdf9d

Author: erichkeane <ekeane at nvidia.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/lib/Parse/ParseOpenACC.cpp

M clang/test/ParserOpenACC/parse-clauses.c

Log Message:

-----------

[OpenACC] Better recover during clause parsing

Previously we gave up immediately and just escaped. Instead, skip to

the next close paren and see if we can continue parsing the next clause

instead.

Commit: aa88a09fbc6428fa3c74e2027b0f329d89c332bd

https://github.com/llvm/llvm-project/commit/aa88a09fbc6428fa3c74e2027b0f329d89c332bd

Author: LLVM GN Syncbot <llvmgnsyncbot at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/utils/gn/secondary/llvm/tools/llvm-exegesis/lib/BUILD.gn

M llvm/utils/gn/secondary/llvm/unittests/tools/llvm-exegesis/BUILD.gn

Log Message:

-----------

[gn build] Port d8b61d716899

Commit: a385c379f8694f42d1efb88bb8c5a53fccb6a664

https://github.com/llvm/llvm-project/commit/a385c379f8694f42d1efb88bb8c5a53fccb6a664

Author: Yitzhak Mandelbaum <ymand at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/lib/Analysis/FlowSensitive/TypeErasedDataflowAnalysis.cpp

Log Message:

-----------

[clang][dataflow] Drop block-relative cap on worklist iterations. (#80033)

As per the FIXME, this cap never really served its purpose. This patch

simplifies to a single, caller-specified, absolute cap.

Commit: 576c4dfa067fa767818a0d80c7072a64c221384e

https://github.com/llvm/llvm-project/commit/576c4dfa067fa767818a0d80c7072a64c221384e

Author: michaelrj-google <71531609+michaelrj-google at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libc/config/linux/x86_64/entrypoints.txt

Log Message:

-----------

[libc] disable epoll_pwait2 due to breakage (#80051)

It appears that sys_epoll_pwait2 isn't always available, so we need to

add some sort of condition to enable it. This patch disables it until

that happens.

Commit: 2c5a0d392592982bb9c73cbc10c64390b9045873

https://github.com/llvm/llvm-project/commit/2c5a0d392592982bb9c73cbc10c64390b9045873

Author: Yitzhak Mandelbaum <ymand at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Analysis/Analyses/PostOrderCFGView.h

M clang/unittests/Analysis/CFGTest.cpp

M clang/unittests/Analysis/FlowSensitive/LoggerTest.cpp

Log Message:

-----------

[clang][CFG] Change child order in Reverse Post Order (RPO) iteration. (#80030)

The CFG orders the blocks of loop bodies before those of loop successors

(both numerically, and in the successor order of the loop condition

block). So, RPO necessarily reverses that order, placing the loop

successor *before* the loop body. For many analyses, particularly those

that converge to a fixpoint, this results in potentially significant

extra work, because loop successors will necessarily need to be

reconsidered once the algorithm has reached a fixpoint on the loop body.

This definition of CFG graph traits reverses the order of children, so

that loop bodies will come first in an RPO. Then, the algorithm can

fully evaluate the loop and only then consider successor blocks.

Commit: 0fa4463e93dca275ee80fd85120e33ccc9f22c5e

https://github.com/llvm/llvm-project/commit/0fa4463e93dca275ee80fd85120e33ccc9f22c5e

Author: Valentin Clement (バレンタイン クレメン) <clementval at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M flang/lib/Semantics/resolve-directives.cpp

M flang/test/Semantics/OpenACC/acc-loop.f90

Log Message:

-----------

[flang][openacc] Check trip count invariance with other IVs (#79906)

2.9.1 The trip count for all loops associated with the collapse clause

must be computable and invariant in all the loops.

This patch checks that iteration range of loops part of a collapse nest

does not depend on outer loops induction variables.

The check is also applied to combined construct with a loop.

Commit: d9423398ea129e229b20ba42dfe4326e620129b5

https://github.com/llvm/llvm-project/commit/d9423398ea129e229b20ba42dfe4326e620129b5

Author: Valentin Clement <clementval at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M flang/lib/Semantics/resolve-directives.cpp

M flang/test/Semantics/OpenACC/acc-loop.f90

Log Message:

-----------

Revert "[flang][openacc] Check trip count invariance with other IVs (#79906)"

This reverts commit 0fa4463e93dca275ee80fd85120e33ccc9f22c5e.

Breaks buildbot https://lab.llvm.org/buildbot/#/builders/268/builds/7155

Commit: 9b91c54d9bd3227a49e146c055fb0165567f7f8d

https://github.com/llvm/llvm-project/commit/9b91c54d9bd3227a49e146c055fb0165567f7f8d

Author: Fangrui Song <i at maskray.me>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Transforms/Instrumentation/MemorySanitizer.cpp

M llvm/test/Instrumentation/MemorySanitizer/msan_asm_conservative.ll

Log Message:

-----------

[msan] Unpoison indirect outputs for userspace using memset for large operands (#79924)

Modify #77393 to clear shadow memory using `llvm.memset.*` when the size

is large, similar to `shouldUseBZeroPlusStoresToInitialize` in clang for

`-ftrivial-auto-var-init=`. The intrinsic, if lowered to libcall, will

use the msan interceptor.

The instruction selector lowers a `StoreInst` to multiple stores, not

utilizing `memset`. When the size is large (e.g.

`store { [100 x i32] } zeroinitializer, ptr %12, align 1`), the

generated code will be long (and `CodeGenPrepare::optimizeInst` will

even crash for a huge size).

```

// Test stack size

template <class T>

void DoNotOptimize(const T& var) { // deprecated by https://github.com/google/benchmark/pull/1493

asm volatile("" : "+m"(const_cast<T&>(var)));

}

int main() {

using LargeArray = std::array<int, 1000000>;

auto large_stack = []() { DoNotOptimize(LargeArray()); };

/////// CodeGenPrepare::optimizeInst triggers an assertion failure when creating an integer type with a bit width>2**23

large_stack();

}

```

Commit: 648560062af8deb4e6478130deb1dd8fa62929a8

https://github.com/llvm/llvm-project/commit/648560062af8deb4e6478130deb1dd8fa62929a8

Author: Fangrui Song <i at maskray.me>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M compiler-rt/lib/dfsan/dfsan_custom.cpp

M compiler-rt/lib/dfsan/done_abilist.txt

M compiler-rt/lib/dfsan/libc_ubuntu1404_abilist.txt

Log Message:

-----------

[dfsan] Wrap glibc 2.38 __isoc23_* functions (#79958)

Fix #79283: `test/dfsan/custom.cpp` has undefined symbol linker errors

on glibc 2.38 due to lack of wrappers for `__isoc23_strtol` and

`__isoc23_scanf` family functions.

Implement these wrappers as aliases to existing wrappers, similar to

https://reviews.llvm.org/D158943 for other sanitizers.

`strtol` in a user program, whether or not `_ISOC2X_SOURCE` is defined,

uses the C23 semantics (`strtol("0b1", 0, 0)` => 1), when

`libclang_rt.dfsan.a` is built on glibc 2.38+.

Commit: a356e6ccada87d6bfc4513fba4b1a682305e094a

https://github.com/llvm/llvm-project/commit/a356e6ccada87d6bfc4513fba4b1a682305e094a

Author: PiJoules <6019989+PiJoules at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/include/llvm/CodeGen/TargetLowering.h

M llvm/lib/CodeGen/SelectionDAG/LegalizeIntegerTypes.cpp

M llvm/lib/CodeGen/SelectionDAG/TargetLowering.cpp

A llvm/test/CodeGen/Thumb/smul_fix.ll

A llvm/test/CodeGen/Thumb/smul_fix_sat.ll

A llvm/test/CodeGen/Thumb/umul_fix.ll

A llvm/test/CodeGen/Thumb/umul_fix_sat.ll

Log Message:

-----------

[SelectionDAG] Expand fixed point multiplication into libcall (#79352)

32-bit ARMv6 with thumb doesn't support MULHS/MUL_LOHI as legal/custom

nodes during expansion which will cause fixed point multiplication of

_Accum types to fail with fixed point arithmetic. Prior to this, we just

happen to use fixed point multiplication on platforms that happen to

support these MULHS/MUL_LOHI.

This patch attempts to check if the multiplication can be done via

libcalls, which are provided by the arm runtime. These libcall attempts

are made elsewhere, so this patch refactors that libcall logic into its

own functions and the fixed point expansion calls and reuses that logic.

Commit: 404af14f92b8b7318ab3d34bd65d800c0bde1e10

https://github.com/llvm/llvm-project/commit/404af14f92b8b7318ab3d34bd65d800c0bde1e10

Author: Maksim Levental <maksim.levental at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M mlir/include/mlir-c/BuiltinTypes.h

M mlir/lib/Bindings/Python/IRTypes.cpp

M mlir/lib/CAPI/IR/BuiltinTypes.cpp

M mlir/python/mlir/dialects/_ods_common.py

M mlir/python/mlir/dialects/memref.py

M mlir/python/mlir/dialects/transform/structured.py

M mlir/test/python/dialects/memref.py

Log Message:

-----------

[mlir][python] enable memref.subview (#79393)

Commit: 24923214e7845acc0e2f56f13e08ee519eba8303

https://github.com/llvm/llvm-project/commit/24923214e7845acc0e2f56f13e08ee519eba8303

Author: Schrodinger ZHU Yifan <yifanzhu at rochester.edu>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libc/config/linux/aarch64/entrypoints.txt

M libc/config/linux/riscv/entrypoints.txt

M libc/config/linux/x86_64/entrypoints.txt

M libc/spec/linux.td

M libc/spec/posix.td

M libc/src/sys/mman/CMakeLists.txt

M libc/src/sys/mman/linux/CMakeLists.txt

A libc/src/sys/mman/linux/mlock.cpp

A libc/src/sys/mman/linux/mlock2.cpp

A libc/src/sys/mman/linux/mlockall.cpp

A libc/src/sys/mman/linux/munlock.cpp

A libc/src/sys/mman/linux/munlockall.cpp

A libc/src/sys/mman/mlock.h

A libc/src/sys/mman/mlock2.h

A libc/src/sys/mman/mlockall.h

A libc/src/sys/mman/munlock.h

A libc/src/sys/mman/munlockall.h

M libc/test/src/sys/mman/linux/CMakeLists.txt

M libc/test/src/sys/mman/linux/mincore_test.cpp

A libc/test/src/sys/mman/linux/mlock_test.cpp

Log Message:

-----------

[libc] implement mlock/mlock2/munlock/mlockall/munlockall (#79645)

fixes #79336

Co-authored-by: Sirui Mu <msrlancern at gmail.com>

Commit: 75ea78ab677f8357aa14fd4c0aff5d551a4ff8aa

https://github.com/llvm/llvm-project/commit/75ea78ab677f8357aa14fd4c0aff5d551a4ff8aa

Author: Felipe de Azevedo Piovezan <fpiovezan at apple.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/include/llvm/DebugInfo/DWARF/DWARFAcceleratorTable.h

M llvm/lib/DebugInfo/DWARF/DWARFAcceleratorTable.cpp

Log Message:

-----------

[DebugNames] Compare TableEntry names more efficiently (#79759)

TableEntry names are pointers into the string table section, and

accessing their

length requires a search for `\0`. However, 99% of the time we only need

to

compare the name against some other other, and such a comparison will

fail as

early as the first character.

This commit adds a method to the interface of TableEntry so that such a

comparison can be done without extracting the full name. It saves 10% in

the

time (1250ms -> 1100 ms) to evaluate the following expression.

```

lldb \

--batch \

-o "b CodeGenFunction::GenerateCode" \

-o run \

-o "expr Fn" \

-- \

clang++ -c -g test.cpp -o /dev/null &> output

```

Commit: e5cebec521a7cf86ff21dedb8a2c96b3f8331c9d

https://github.com/llvm/llvm-project/commit/e5cebec521a7cf86ff21dedb8a2c96b3f8331c9d

Author: jkorous-apple <32549412+jkorous-apple at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/lib/Analysis/UnsafeBufferUsage.cpp

Log Message:

-----------

[-Wunsafe-buffer-usage] Fix AST matcher of UUCAddAssignGadget (#79392)

We are not interested in nonpointers being added to.

Commit: bb770f0df53eee91a803b2829808d82279f7b577

https://github.com/llvm/llvm-project/commit/bb770f0df53eee91a803b2829808d82279f7b577

Author: yronglin <yronglin777 at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/include/clang/AST/TextNodeDumper.h

M clang/lib/AST/TextNodeDumper.cpp

M clang/test/AST/ast-dump-for-range-lifetime.cpp

M clang/test/Import/cxx-default-init-expr/test.cpp

Log Message:

-----------

[Clang] Dump the rewritten sub-expressions in CXXDefaultArgExpr/CXXDefaultInitExpr (#80001)

This patch dump the rewritten sub-expressions in `CXXDefaultArgExpr` and

`CXXDefaultInitExpr`.

This machinery is useful for checking whether the materialized

temporaries is lifetime-extended in the sub-AST of `CXXDefaultArgExpr`

(`CXXDefaultInitExpr` has not been lifetime extendend now).

Signed-off-by: yronglin <yronglin777 at gmail.com>

Commit: 2f490f924647aa0724bab49cb390d4423fc9fc03

https://github.com/llvm/llvm-project/commit/2f490f924647aa0724bab49cb390d4423fc9fc03

Author: Valentin Clement <clementval at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M flang/lib/Semantics/resolve-directives.cpp

M flang/test/Semantics/OpenACC/acc-loop.f90

Log Message:

-----------

[flang][openacc] Check trip count invariance with other IVs (#79906)

2.9.1 The trip count for all loops associated with the collapse clause must be

computable and invariant in all the loops.

This patch checks that loops part of a collapse nest does not depends on outer

loops induction variables.

The check is also applied to combined construct with a loop.

Commit: 16c15b5f84836d81084e9987701ca011da5a864f

https://github.com/llvm/llvm-project/commit/16c15b5f84836d81084e9987701ca011da5a864f

Author: Nick Desaulniers <nickdesaulniers at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M libc/test/src/sys/mman/linux/mlock_test.cpp

Log Message:

-----------

[libc] disable mlockall w/ MCL_ONFAULT (#80075)

I suspect this is a bug in linux 4.19, as the test passes as written on

my

linux 6.5 machine.

Let's revisit this after the build bots are upgraded.

Link: #80073

Commit: 7847e44594aa932c0a5f5d2cd15940d2a815c059

https://github.com/llvm/llvm-project/commit/7847e44594aa932c0a5f5d2cd15940d2a815c059

Author: Michael Spencer <bigcheesegs at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Basic/DiagnosticSerializationKinds.td

M clang/include/clang/Basic/FileManager.h

M clang/include/clang/Lex/HeaderSearch.h

M clang/include/clang/Lex/HeaderSearchOptions.h

M clang/include/clang/Serialization/ASTBitCodes.h

M clang/include/clang/Serialization/ASTReader.h

M clang/include/clang/Serialization/ASTWriter.h

M clang/include/clang/Serialization/ModuleFile.h

M clang/include/clang/Tooling/DependencyScanning/DependencyScanningFilesystem.h

M clang/include/clang/Tooling/DependencyScanning/DependencyScanningService.h

M clang/lib/Basic/FileManager.cpp

M clang/lib/Frontend/CompilerInvocation.cpp

M clang/lib/Lex/HeaderSearch.cpp

M clang/lib/Serialization/ASTReader.cpp

M clang/lib/Serialization/ASTWriter.cpp

M clang/lib/Tooling/DependencyScanning/DependencyScanningFilesystem.cpp

M clang/lib/Tooling/DependencyScanning/DependencyScanningWorker.cpp

M clang/lib/Tooling/DependencyScanning/ModuleDepCollector.cpp

A clang/test/ClangScanDeps/optimize-vfs-edgecases.m

A clang/test/ClangScanDeps/optimize-vfs-leak.m

A clang/test/ClangScanDeps/optimize-vfs-pch.m

A clang/test/ClangScanDeps/optimize-vfs.m

M clang/tools/clang-scan-deps/ClangScanDeps.cpp

M llvm/include/llvm/Support/VirtualFileSystem.h

M llvm/lib/Support/VirtualFileSystem.cpp

M llvm/unittests/Support/VirtualFileSystemTest.cpp

Log Message:

-----------

[clang][DependencyScanner] Remove unused -ivfsoverlay files (#73734)

`-ivfsoverlay` files are unused when building most modules. Enable

removing them by,

* adding a way to visit the filesystem tree with extensible RTTI to

access each `RedirectingFileSystem`.

* Adding tracking to `RedirectingFileSystem` to record when it

actually redirects a file access.

* Storing this information in each PCM.

Usage tracking is only enabled when iterating over the source manager

and affecting modulemaps. Here each path is stated to cause an access.

During scanning these stats all hit the cache.

Commit: 86cd2fbdfe67d70a7fe061ed5d3a644f50f070f5

https://github.com/llvm/llvm-project/commit/86cd2fbdfe67d70a7fe061ed5d3a644f50f070f5

Author: jkorous-apple <32549412+jkorous-apple at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/test/SemaCXX/warn-unsafe-buffer-usage-fixits-pointer-access.cpp

Log Message:

-----------

[-Wunsafe-buffer-usage][NFC] Add testcase for non-unsafe pointer (#80076)

This adds a missing CHECK-NOT directive for an existing test case.

Commit: c8c3fe70ae09a48408ee15a256e52a4624e0291c

https://github.com/llvm/llvm-project/commit/c8c3fe70ae09a48408ee15a256e52a4624e0291c

Author: Jacek Caban <jacek at codeweavers.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M lld/COFF/DLL.cpp

M lld/test/COFF/imports.test

M lld/test/COFF/pdb-publics-import.test

Log Message:

-----------

[LLD][COFF] Align import directory chunk. (#80014)

The loader can usually handle an unaligned import dir chunk, but It's not

optimal and it's not what MSVC link.exe does.

Windows refuses to load ARM64X binaries with unaligned import directory.

aarch64 and arm64ec imports are shared in such binaries as much as

possible. As long as they use the same set of functions from given import

directory, both the directory and import addresses chunk are just shared.

When used set of functions differs, ARM64X dynamic relocations are used

to modify import dir to point to different names and import addresses for

its EC view. I suspect that the loader expects some alignment on ARM64X

dynamic relocation offset and may not be the case when relocated import

dir is not aligned.

Commit: 8b38970811086b09752a5909d0c17de4d0cd04c3

https://github.com/llvm/llvm-project/commit/8b38970811086b09752a5909d0c17de4d0cd04c3

Author: Katherine Rasmussen <krasmussen at lbl.gov>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M flang/docs/Intrinsics.md

M flang/lib/Evaluate/intrinsics.cpp

M flang/lib/Semantics/check-call.cpp

A flang/test/Semantics/image_index01.f90

A flang/test/Semantics/image_index02.f90

Log Message:

-----------

[flang] Add image_index to list of intrinsics and add tests (#79519)

Add image_index to the list of intrinsic functions and add additional

check on its args in check-call.cpp. Add two semantics tests for

image_index.

Commit: 4effff21fb2f3462e06fcbd7812562f4771b0487

https://github.com/llvm/llvm-project/commit/4effff21fb2f3462e06fcbd7812562f4771b0487

Author: Kai Sasaki <lewuathe at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M mlir/lib/Conversion/ComplexToStandard/ComplexToStandard.cpp

M mlir/test/Conversion/ComplexToStandard/convert-to-standard.mlir

M mlir/test/Conversion/ComplexToStandard/full-conversion.mlir

M mlir/test/Integration/Dialect/Complex/CPU/correctness.mlir

Log Message:

-----------

[mlir][complex] Prevent underflow in complex.abs (#79786)

The previous PR was not correct on the way to handle the negative value.

It is necessary to take the absolute value of the given real (or

imaginary) part to be multiplied with the sqrt part.

See: https://github.com/llvm/llvm-project/pull/76316

Commit: b21a2f9365b6c5fd464a97be5dfe7085742870ef

https://github.com/llvm/llvm-project/commit/b21a2f9365b6c5fd464a97be5dfe7085742870ef

Author: Michael Spencer <bigcheesegs at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/lib/Tooling/DependencyScanning/DependencyScanningWorker.cpp

A clang/test/ClangScanDeps/missing-vfs.m

Log Message:

-----------

[clang][scan-deps] Stop scanning if any scanning setup emits an error.

Without this scanning will continue and later hit an assert that the

number of `RedirectingFileSystem`s matches the number of -ivfsoverlay

arguments.

Commit: c806d8c7e948f01405be4ea344d883f066f8ae59

https://github.com/llvm/llvm-project/commit/c806d8c7e948f01405be4ea344d883f066f8ae59

Author: rmarker <37921131+rmarker at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/docs/tools/dump_format_style.py

Log Message:

-----------

[clang-format] Explicitly open DOC_FILE with utf-8 in dump_format_style.py (#79805)

The dump_format_style.py script generates the clang-format style options

documentation.

There was an issue where the script could include spurious characters in

the output when run in windows. It appears that it wasn't defaulting to

the correct encoding when reading the input.

This has been addressed by explicitly setting the encoding when opening

the file.

Commit: b91bba89edfb25d011e1f2366cda5dec605c87f6

https://github.com/llvm/llvm-project/commit/b91bba89edfb25d011e1f2366cda5dec605c87f6

Author: Jakub Kuderski <jakub at nod-labs.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M mlir/include/mlir/Conversion/MemRefToSPIRV/MemRefToSPIRV.h

M mlir/lib/Conversion/GPUToSPIRV/GPUToSPIRVPass.cpp

M mlir/lib/Conversion/MemRefToSPIRV/MapMemRefStorageClassPass.cpp

Log Message:

-----------

[mlir][spirv] Use `AttrTypeReplacer` in map-memref-storage-class. NFC. (#80055)

Keep the conversion target to allow for checking if the op is legal.

Commit: d783933bc910ac005e18928d22b6c10c4fe8d6f6

https://github.com/llvm/llvm-project/commit/d783933bc910ac005e18928d22b6c10c4fe8d6f6

Author: Yaraslau <yaraslau.tamashevich at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

A clang/test/ClangScanDeps/empty.cpp

M clang/tools/clang-scan-deps/ClangScanDeps.cpp

Log Message:

-----------

[clang-scan-deps] Fix check for empty `Compilation` (#75545)

Closes https://github.com/llvm/llvm-project/issues/64144

Instead of checking for `nullptr` we need to ensure that `JobList` is

not empty to proceed

Commit: 2abcbbd96ad731b05fae970a0abb23cda784dddd

https://github.com/llvm/llvm-project/commit/2abcbbd96ad731b05fae970a0abb23cda784dddd

Author: Maksim Panchenko <maks at fb.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M bolt/include/bolt/Core/BinaryContext.h

M bolt/include/bolt/Utils/CommandLineOpts.h

M bolt/lib/Profile/DataAggregator.cpp

M bolt/lib/Rewrite/LinuxKernelRewriter.cpp

M bolt/lib/Rewrite/RewriteInstance.cpp

M bolt/lib/Utils/CommandLineOpts.cpp

M bolt/test/X86/linux-orc.s

Log Message:

-----------

[BOLT] Detect Linux kernel based on ELF program headers (#80086)

Check if program header addresses fall into the kernel space to detect a

Linux kernel binary on x86-64.

Delete opts::LinuxKernelMode and use BinaryContext::IsLinuxKernel

instead.

Commit: b4d832c77dcba4136132559a5183883cf064389d

https://github.com/llvm/llvm-project/commit/b4d832c77dcba4136132559a5183883cf064389d

Author: Carl Peto <carl.peto at me.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Sema/Sema.h

M clang/lib/Parse/ParseExpr.cpp

M clang/lib/Parse/ParseObjc.cpp

M clang/lib/Sema/SemaDecl.cpp

Log Message:

-----------

[clang] Improved isSimpleTypeSpecifier (#79037)

- Sema::isSimpleTypeSpecifier return true for _Bool in c99 (currently

returns false for _Bool, regardless of C dialect). (Fixes #72203)

- replace the logic with a check for simple types and a proper check for

a valid keyword in the appropriate dialect

Co-authored-by: Carl Peto <CPeto at becrypt.com>

Commit: c761b4a5e4cc003a2c850898e1dc67d2637cfb0c

https://github.com/llvm/llvm-project/commit/c761b4a5e4cc003a2c850898e1dc67d2637cfb0c

Author: Billy Laws <blaws05 at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/AArch64/AArch64ISelLowering.cpp

M llvm/test/CodeGen/AArch64/arm64ec-varargs.ll

M llvm/test/CodeGen/AArch64/vararg-tallcall.ll

Log Message:

-----------

[AArch64] Fix variadic tail-calls on ARM64EC (#79774)

ARM64EC varargs calls expect that x4 = sp at entry, special handling is

needed to ensure this with tail calls since they occur after the

epilogue and the x4 write happens before.

I tried going through AArch64MachineFrameLowering for this, hoping to

avoid creating the dummy object but this was the best I could do since

the stack info that uses isn't populated at this stage,

CreateFixedObject also explicitly forbids 0 sized objects.

Commit: 1a17f2beb9cd1f5bbaa64502ab5c02ff74c199a4

https://github.com/llvm/llvm-project/commit/1a17f2beb9cd1f5bbaa64502ab5c02ff74c199a4

Author: Congcong Cai <congcongcai0907 at 163.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/WebAssembly/WebAssemblyTargetMachine.cpp

A llvm/test/CodeGen/WebAssembly/disable-feature.ll

Log Message:

-----------

[WebAssembly] avoid to use explicit disabled feature

In `CoalesceFeaturesAndStripAtomics`, feature string is converted to FeatureBitset and back to feature string. It will lose information about explicit diasbled features.

Commit: c43fda3efcbf5b16e611473cf03c88381237f50f

https://github.com/llvm/llvm-project/commit/c43fda3efcbf5b16e611473cf03c88381237f50f

Author: Congcong Cai <congcongcai0907 at 163.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/WebAssembly/WebAssemblyTargetMachine.cpp

R llvm/test/CodeGen/WebAssembly/disable-feature.ll

Log Message:

-----------

Revert "[WebAssembly] avoid to use explicit disabled feature"

This reverts commit 1a17f2beb9cd1f5bbaa64502ab5c02ff74c199a4.

Commit: ff4636a4ab00b633c15eb3942c26126ceb2662e6

https://github.com/llvm/llvm-project/commit/ff4636a4ab00b633c15eb3942c26126ceb2662e6

Author: Oskar Wirga <10386631+oskarwirga at users.noreply.github.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/include/llvm/CodeGen/LivePhysRegs.h

M llvm/include/llvm/CodeGen/MachineBasicBlock.h

M llvm/lib/CodeGen/BranchFolding.cpp

M llvm/lib/Target/AArch64/AArch64FrameLowering.cpp

M llvm/lib/Target/AArch64/AArch64InstrInfo.cpp

M llvm/lib/Target/ARM/ARMLowOverheadLoops.cpp

M llvm/lib/Target/PowerPC/PPCExpandAtomicPseudoInsts.cpp

M llvm/lib/Target/PowerPC/PPCFrameLowering.cpp

M llvm/lib/Target/SystemZ/SystemZFrameLowering.cpp

M llvm/lib/Target/X86/X86FrameLowering.cpp

M llvm/test/CodeGen/SystemZ/branch-folder-hoist-livein.mir

M llvm/test/CodeGen/Thumb2/LowOverheadLoops/spillingmove.mir

Log Message:

-----------

Refactor recomputeLiveIns to converge on added MachineBasicBlocks (#79940)

This is a fix for the regression seen in

https://github.com/llvm/llvm-project/pull/79498

> Currently, the way that recomputeLiveIns works is that it will

recompute the livein registers for that MachineBasicBlock but it matters

what order you call recomputeLiveIn which can result in incorrect

register allocations down the line.

Now we do not recompute the entire CFG but we do ensure that the newly

added MBB do reach convergence.

Commit: c19436eec1c236cbe622c04e33f35f1f9478fa15

https://github.com/llvm/llvm-project/commit/c19436eec1c236cbe622c04e33f35f1f9478fa15

Author: Kohei Yamaguchi <fix7211 at gmail.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M mlir/lib/Conversion/SPIRVToLLVM/SPIRVToLLVM.cpp

Log Message:

-----------

[mlir][spirv] Fix a crash of typeConverter with non supported type (#79955)

Fixes a crash in the `convert-to-spirv-llvm` pass caused by unsupported

types (e.g. `spirv.matrix` ). This PR fixes it by checking the converted type.

Fixes #60017

Commit: 7155c1ef658b66132f15bf1406e84e68eed3358f

https://github.com/llvm/llvm-project/commit/7155c1ef658b66132f15bf1406e84e68eed3358f

Author: Joseph Huber <huberjn at outlook.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang/include/clang/Basic/DiagnosticDriverKinds.td

M clang/lib/Basic/Targets/NVPTX.cpp

M clang/lib/Basic/Targets/NVPTX.h

M clang/lib/Driver/ToolChains/Cuda.cpp

M clang/test/Driver/cuda-cross-compiling.c

M clang/test/Preprocessor/predefined-arch-macros.c

Log Message:

-----------

[NVPTX] Allow compiling LLVM-IR without `-march` set (#79873)

Summary:

The NVPTX tools require an architecture to be used, however if we are

creating generic LLVM-IR we should be able to leave it unspecified. This

will result in the `target-cpu` attributes not being set on the

functions so it can be changed when linked into code. This allows the

standalone `--target=nvptx64-nvidia-cuda` toolchain to create LLVM-IR

simmilar to how CUDA's deviceRTL looks from C/C++

Commit: ab70ac605e784c630122b27c5971fde68e80bd1b

https://github.com/llvm/llvm-project/commit/ab70ac605e784c630122b27c5971fde68e80bd1b

Author: Younan Zhang <zyn7109 at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/docs/ReleaseNotes.rst

M clang/lib/AST/DeclTemplate.cpp

M clang/lib/Sema/SemaConcept.cpp

M clang/test/SemaTemplate/concepts-out-of-line-def.cpp

Log Message:

-----------

[concepts] Push a CurContext before substituting into out-of-line constraints for comparison (#79985)

Commit: fa3307eb3f47b0bd574fc754934f98c0f27e4e36

https://github.com/llvm/llvm-project/commit/fa3307eb3f47b0bd574fc754934f98c0f27e4e36

Author: Karthika Devi C <quic_kartc at quicinc.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M polly/lib/Analysis/ScopBuilder.cpp

A polly/test/ScopInfo/reduction_different_index.ll

A polly/test/ScopInfo/reduction_different_index1.ll

Log Message:

-----------

[polly] Make reduction detection checks more robust - part 1 (#75297)

Existing reduction detection algorithm does two types of memory checks

before marking a load store pair as reduction.

First is to check if load and store are pointing to the same memory. This

check right now detects the following case as reduction. sum[0] = sum[1]

+ A[i]

This is because the check compares only base of the memory addresses

involved and not their indices. This patch addresses this issue and

introduces some debug prints. Added couple of test cases to verify the

functionality of patch as well.

Commit: 9179d87abce8e92c0bf30bc1ee1c17e17e362bc0

https://github.com/llvm/llvm-project/commit/9179d87abce8e92c0bf30bc1ee1c17e17e362bc0

Author: Craig Topper <craig.topper at sifive.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/RISCV/RISCVISelLowering.cpp

M llvm/lib/Target/RISCV/RISCVISelLowering.h

Log Message:

-----------

[RISCV] Remove unused RISCVISD opcodes. NFC

These were left behind after fb94c6491a114ebd5815b1d42665a8f6bcd9d639

Commit: 150ab99583e252a809b94f89da2576a1fc808297

https://github.com/llvm/llvm-project/commit/150ab99583e252a809b94f89da2576a1fc808297

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/X86/X86InstrInfo.h

Log Message:

-----------

[X86][NFC] Add documentation for methods in X86InstrInfo.h

Address RKSimon's comment in 2960656eb909b5361ce2c3f641ee341769076ab7

Commit: c12f30c7ffedb2338d64d8f98a76ae56c497cfbb

https://github.com/llvm/llvm-project/commit/c12f30c7ffedb2338d64d8f98a76ae56c497cfbb

Author: Ben Shi <2283975856 at qq.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/lib/StaticAnalyzer/Checkers/StdLibraryFunctionsChecker.cpp

M clang/test/Analysis/errno-stdlibraryfunctions.c

Log Message:

-----------

[clang][analyzer] Improve modeling of 'realpath' in StdLibraryFunctionsChecker (#79939)

Commit: 8e77390c065fafeca220937e28f7d2ecc1a9ef15

https://github.com/llvm/llvm-project/commit/8e77390c065fafeca220937e28f7d2ecc1a9ef15

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/X86/X86InstrAVX512.td

M llvm/lib/Target/X86/X86InstrFoldTables.cpp

M llvm/lib/Target/X86/X86InstrFoldTables.h

M llvm/lib/Target/X86/X86InstrInfo.cpp

M llvm/lib/Target/X86/X86InstrInfo.h

M llvm/test/CodeGen/X86/vector-interleaved-load-i16-stride-7.ll

M llvm/test/CodeGen/X86/vector-interleaved-store-i16-stride-5.ll

M llvm/test/CodeGen/X86/vector-interleaved-store-i8-stride-8.ll

Log Message:

-----------

[X86][CodeGen] Support folding memory broadcast in X86InstrInfo::foldMemoryOperandImpl (#79761)

Commit: a034e65e972175a2465deacb8c78bc7efc99bd23

https://github.com/llvm/llvm-project/commit/a034e65e972175a2465deacb8c78bc7efc99bd23

Author: Yingwei Zheng <dtcxzyw2333 at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Transforms/Scalar/CorrelatedValuePropagation.cpp

M llvm/test/Transforms/CorrelatedValuePropagation/basic.ll

A llvm/test/Transforms/CorrelatedValuePropagation/switch.ll

Log Message:

-----------

[CVP] Check whether the default case is reachable (#79993)

This patch eliminates unreachable default cases using context-sensitive

range information.

Commit: 5d7a0a734a0073ed2237606558d7616923ff50c2

https://github.com/llvm/llvm-project/commit/5d7a0a734a0073ed2237606558d7616923ff50c2

Author: Kazu Hirata <kazu at google.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/X86/X86InstrInfo.cpp

Log Message:

-----------

[X86] Use a range-based for loop (NFC)

Commit: eef6485ac1bffb6adf0b25ff4a117aa1590e70d0

https://github.com/llvm/llvm-project/commit/eef6485ac1bffb6adf0b25ff4a117aa1590e70d0

Author: Kazu Hirata <kazu at google.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/AMDGPU/R600OptimizeVectorRegisters.cpp

Log Message:

-----------

[AMDGPU] Use llvm::all_of (NFC)

Commit: 2699c1d7007ea8001bfaae50de01ff33791ce958

https://github.com/llvm/llvm-project/commit/2699c1d7007ea8001bfaae50de01ff33791ce958

Author: Kazu Hirata <kazu at google.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M clang-tools-extra/clang-tidy/bugprone/ReservedIdentifierCheck.cpp

Log Message:

-----------

[clang-tidy] Use StringRef::starts_with (NFC)

Commit: 292b508ebaa653073d9ce12156c93f5a0cf67680

https://github.com/llvm/llvm-project/commit/292b508ebaa653073d9ce12156c93f5a0cf67680

Author: Kazu Hirata <kazu at google.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/AMDGPU/AsmParser/AMDGPUAsmParser.cpp

Log Message:

-----------

[AMDGPU] Use StringRef::consume_front (NFC)

Commit: 8a98091162841fabc3816f3f29380c930ccbcab5

https://github.com/llvm/llvm-project/commit/8a98091162841fabc3816f3f29380c930ccbcab5

Author: Craig Topper <craig.topper at sifive.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/lib/Target/RISCV/RISCVInstrInfo.td

M llvm/test/CodeGen/RISCV/or-is-add.ll

M llvm/test/CodeGen/RISCV/rv64-legal-i32/rv64zba.ll

M llvm/test/CodeGen/RISCV/rv64zba.ll

Log Message:

-----------

[RISCV] Use disjoint flag in or_is_add.

Commit: f2816ff60c7dae0347beba9b11154b33e6311059

https://github.com/llvm/llvm-project/commit/f2816ff60c7dae0347beba9b11154b33e6311059

Author: Yingwei Zheng <dtcxzyw2333 at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineAndOrXor.cpp

M llvm/test/Transforms/InstCombine/and-or-icmps.ll

M llvm/test/Transforms/InstCombine/and-or-not.ll

M llvm/test/Transforms/InstCombine/and-xor-or.ll

M llvm/test/Transforms/InstCombine/or-xor.ll

M llvm/test/Transforms/InstCombine/or.ll

Log Message:

-----------

[InstCombine] Simplify and/or by replacing operands with constants (#77231)

This patch tries to simplify `X | Y` by replacing occurrences of `Y` in

`X` with 0. Similarly, it tries to simplify `X & Y` by replacing

occurrences of `Y` in `X` with -1.

Alive2: https://alive2.llvm.org/ce/z/cNjDTR

Note: As the current implementation is too conservative in the one-use

checks, I cannot remove other existing hard-coded simplifications if

they involves more than two instructions (e.g, `A & ~(A ^ B) --> A &

B`).

Compile-time impact:

http://llvm-compile-time-tracker.com/compare.php?from=a085402ef54379758e6c996dbaedfcb92ad222b5&to=9d655c6685865ffce0ad336fed81228f3071bd03&stat=instructions%3Au

|stage1-O3|stage1-ReleaseThinLTO|stage1-ReleaseLTO-g|stage1-O0-g|stage2-O3|stage2-O0-g|stage2-clang|

|--|--|--|--|--|--|--|

|+0.01%|-0.00%|+0.00%|-0.02%|+0.01%|+0.02%|-0.01%|

Fixes #76554.

Commit: 5bb99edcb6726e5dcc20d2236ef51b11c248acb9

https://github.com/llvm/llvm-project/commit/5bb99edcb6726e5dcc20d2236ef51b11c248acb9

Author: Timm Baeder <tbaeder at redhat.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/lib/AST/Interp/ByteCodeExprGen.cpp

M clang/lib/AST/Interp/ByteCodeExprGen.h

M clang/lib/AST/Interp/Descriptor.cpp

M clang/lib/AST/Interp/Descriptor.h

M clang/lib/AST/Interp/Interp.cpp

M clang/lib/AST/Interp/Interp.h

M clang/lib/AST/Interp/InterpFrame.cpp

M clang/lib/AST/Interp/Opcodes.td

M clang/lib/AST/Interp/Pointer.cpp

M clang/lib/AST/Interp/Pointer.h

M clang/lib/AST/Interp/Program.cpp

M clang/test/AST/Interp/cxx11.cpp

M clang/test/AST/Interp/cxx17.cpp

M clang/test/AST/Interp/cxx23.cpp

M clang/test/AST/Interp/literals.cpp

M clang/unittests/AST/Interp/Descriptor.cpp

Log Message:

-----------

[clang][Interp] Add inline descriptor to global variables (#72892)

Some time ago, I did a similar patch for local variables.

Initializing global variables can fail as well:

```c++

constexpr int a = 1/0;

static_assert(a == 0);

```

... would succeed in the new interpreter, because we never saved the

fact that `a` has not been successfully initialized.

Commit: 6f35f1d7c137f5733b7035444397bcdace5c9df1

https://github.com/llvm/llvm-project/commit/6f35f1d7c137f5733b7035444397bcdace5c9df1

Author: Piggy <piggynl at outlook.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M .git-blame-ignore-revs

Log Message:

-----------

[NFC] Update .git-blame-ignore-revs for compiler-rt builtins (#79803)

The three commits from "[RFC] compiler-rt builtins cleanup and

refactoring" rewrote lots of code in compiler-rt builtins.

- 082b89b: [builtins] Reformat builtins with clang-format

- 0ba22f5: [builtins] Use single line C++/C99 comment style

- 84da0e1: [builtins] Use aliases for function redirects

Commit: 95947465024e865a4a671e94902db40d250f0601

https://github.com/llvm/llvm-project/commit/95947465024e865a4a671e94902db40d250f0601

Author: Piggy <piggynl at outlook.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M .github/new-prs-labeler.yml

Log Message:

-----------

[NFC] Add compiler-rt:* to .github/new-prs-labeler.yml (#79872)

After this change, all current compiler-rt:* labels on GitHub are

covered.

Commit: c83ec847ac9d06fb4ad85ce3bc50d7a6b122ead2

https://github.com/llvm/llvm-project/commit/c83ec847ac9d06fb4ad85ce3bc50d7a6b122ead2

Author: martinboehme <mboehme at google.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/lib/Analysis/FlowSensitive/DataflowEnvironment.cpp

Log Message:

-----------

[clang][dataflow] Extend debug output for `Environment`. (#79982)

* Print `ReturnLoc`, `ReturnVal`, and `ThisPointeeLoc` if applicable.

* For entries in `LocToVal` that correspond to declarations, print the

names

of the declarations next to them.

I've removed the FIXME because all relevant fields are now being dumped.

I'm

not sure we actually need the capability for the caller to specify which

fields

to dump, so I've simply deleted this part of the comment.

Some examples of the output:

Commit: 3564666fe19217e3d6d3d98dd182553fc8d50e6f

https://github.com/llvm/llvm-project/commit/3564666fe19217e3d6d3d98dd182553fc8d50e6f

Author: Changpeng Fang <changpeng.fang at amd.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/test/Analysis/UniformityAnalysis/AMDGPU/intrinsics.ll

M llvm/test/CodeGen/AMDGPU/llvm.amdgcn.wmma_64.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w32-f16-f32-matrix-modifiers.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w32-imm.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w32-iu-modifiers.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w32-swmmac-index_key.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w32.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w64-f16-f32-matrix-modifiers.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w64-imm.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w64-iu-modifiers.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w64-swmmac-index_key.ll

M llvm/test/CodeGen/AMDGPU/wmma-gfx12-w64.ll

M llvm/test/CodeGen/AMDGPU/wmma_modifiers.ll

M llvm/test/CodeGen/AMDGPU/wmma_multiple_32.ll

M llvm/test/CodeGen/AMDGPU/wmma_multiple_64.ll

Log Message:

-----------

[AMDGPU]: Fix type signatures for wmma intrinsics, NFC (#80087)

Make the wmma intrinsic type signatures to be canonical. We need

a type signature as long as the type is not fixed. However, when an

argument's type matches a previous argument's type, we do not need the

signature for this argument.

This patch fixes three general cases:

1. add missing signatures

2. remove signatures for matching arguments

3. reorer the signatures -- return type signature should always appear

first

Commit: ee01a2c3996f9647f3158f5acdb921a6ede94dc1

https://github.com/llvm/llvm-project/commit/ee01a2c3996f9647f3158f5acdb921a6ede94dc1

Author: Tianlan Zhou <bobby825 at 126.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang-tools-extra/clangd/InlayHints.cpp

M clang/docs/ReleaseNotes.rst

M clang/lib/AST/ExprConstant.cpp

M clang/lib/CodeGen/CGExpr.cpp

M clang/lib/Sema/SemaChecking.cpp

M clang/lib/Sema/SemaOverload.cpp

A clang/test/AST/ast-dump-static-operators.cpp

M clang/test/CodeGenCXX/cxx2b-static-call-operator.cpp

M clang/test/CodeGenCXX/cxx2b-static-subscript-operator.cpp

A clang/test/SemaCXX/cxx2b-static-operator.cpp

Log Message:

-----------

[clang] static operators should evaluate object argument (reland) (#80108)

This re-applies 30155fc0 with a fix for clangd.

### Description

clang don't evaluate the object argument of `static operator()` and

`static operator[]` currently, for example:

```cpp

#include <iostream>

struct Foo {

static int operator()(int x, int y) {

std::cout << "Foo::operator()" << std::endl;

return x + y;

}

static int operator[](int x, int y) {

std::cout << "Foo::operator[]" << std::endl;

return x + y;

}

};

Foo getFoo() {

std::cout << "getFoo()" << std::endl;

return {};

}

int main() {

std::cout << getFoo()(1, 2) << std::endl;

std::cout << getFoo()[1, 2] << std::endl;

}

```

`getFoo()` is expected to be called, but clang don't call it currently

(17.0.6). This PR fixes this issue.

Fixes #67976, reland #68485.

### Walkthrough

- **clang/lib/Sema/SemaOverload.cpp**

- **`Sema::CreateOverloadedArraySubscriptExpr` &

`Sema::BuildCallToObjectOfClassType`**

Previously clang generate `CallExpr` for static operators, ignoring the

object argument. In this PR `CXXOperatorCallExpr` is generated for

static operators instead, with the object argument as the first

argument.

- **`TryObjectArgumentInitialization`**

`const` / `volatile` objects are allowed for static methods, so that we

can call static operators on them.

- **clang/lib/CodeGen/CGExpr.cpp**

- **`CodeGenFunction::EmitCall`**

CodeGen changes for `CXXOperatorCallExpr` with static operators: emit

and ignore the object argument first, then emit the operator call.

- **clang/lib/AST/ExprConstant.cpp**

- **`ExprEvaluatorBase::handleCallExpr`**

Evaluation of static operators in constexpr also need some small changes

to work, so that the arguments won't be out of position.

- **clang/lib/Sema/SemaChecking.cpp**

- **`Sema::CheckFunctionCall`**

Code for argument checking also need to be modify, or it will fail the

test `clang/test/SemaCXX/overloaded-operator-decl.cpp`.

- **clang-tools-extra/clangd/InlayHints.cpp**

- **`InlayHintVisitor::VisitCallExpr`**

Now that the `CXXOperatorCallExpr` for static operators also have object

argument, we should also take care of this situation in clangd.

### Tests

- **Added:**

- **clang/test/AST/ast-dump-static-operators.cpp**

Verify the AST generated for static operators.

- **clang/test/SemaCXX/cxx2b-static-operator.cpp**

Static operators should be able to be called on const / volatile

objects.

- **Modified:**

- **clang/test/CodeGenCXX/cxx2b-static-call-operator.cpp**

- **clang/test/CodeGenCXX/cxx2b-static-subscript-operator.cpp**

Matching the new CodeGen.

### Documentation

- **clang/docs/ReleaseNotes.rst**

Update release notes.

---------

Co-authored-by: Shafik Yaghmour <shafik at users.noreply.github.com>

Co-authored-by: cor3ntin <corentinjabot at gmail.com>

Co-authored-by: Aaron Ballman <aaron at aaronballman.com>

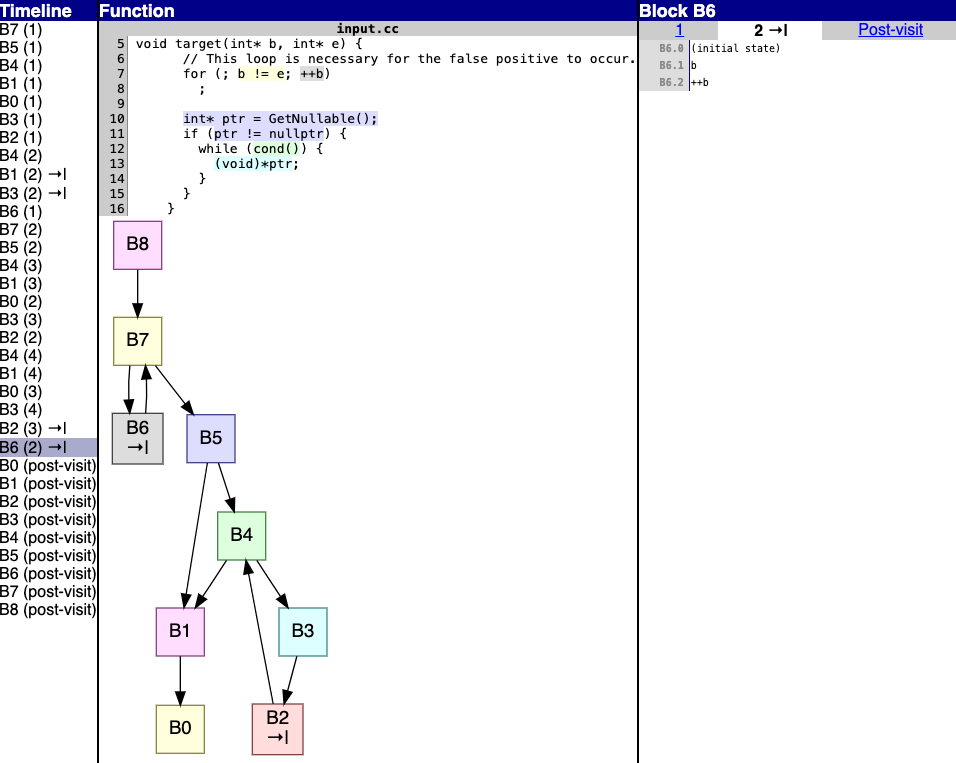

Commit: 82324bc991401aecc4d743d4993b6c68dd60a615

https://github.com/llvm/llvm-project/commit/82324bc991401aecc4d743d4993b6c68dd60a615

Author: martinboehme <mboehme at google.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/lib/Analysis/FlowSensitive/HTMLLogger.cpp

Log Message:

-----------

[clang][dataflow] In the CFG visualization, mark converged blocks. (#79999)

Here's an example of the output:

Commit: b49b3ddd828192f0b3ef43762ab832b085ac95c4

https://github.com/llvm/llvm-project/commit/b49b3ddd828192f0b3ef43762ab832b085ac95c4

Author: Kazu Hirata <kazu at google.com>

Date: 2024-01-30 (Tue, 30 Jan 2024)

Changed paths:

M llvm/include/llvm/ADT/SmallPtrSet.h

Log Message:

-----------

[ADT] Use a constexpr version of llvm::bit_ceil (NFC) (#79709)

This patch replaces the template trick with a constexpr function that

is more readable. Once C++20 is available in our code base, we can

remove the constexpr function in favor of std::bit_ceil.

Commit: f292f90bc2ec2c1ec4306027e17877bb4603d8d2

https://github.com/llvm/llvm-project/commit/f292f90bc2ec2c1ec4306027e17877bb4603d8d2

Author: Yingwei Zheng <dtcxzyw2333 at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineSelect.cpp

M llvm/test/Transforms/InstCombine/fabs.ll

Log Message:

-----------

[InstCombine] Fold select with signbit idiom into fabs (#76342)

This patch folds:

```

((bitcast X to int) <s 0 ? -X : X) -> fabs(X)

((bitcast X to int) >s -1 ? X : -X) -> fabs(X)

((bitcast X to int) <s 0 ? X : -X) -> -fabs(X)

((bitcast X to int) >s -1 ? -X : X) -> -fabs(X)

```

Alive2: https://alive2.llvm.org/ce/z/rGepow

Commit: d71831a2172e4cf7c3f3540c472ce2aeb14d4505

https://github.com/llvm/llvm-project/commit/d71831a2172e4cf7c3f3540c472ce2aeb14d4505

Author: Chuanqi Xu <yedeng.yd at linux.alibaba.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/test/Interpreter/cxx20-modules.cppm

Log Message:

-----------

[NFC] [clang-repl] Fix test failures due to incosistent target settings

See https://github.com/llvm/llvm-project/pull/79261 for details.

It shows that clang-repl uses a different target triple with clang so that it

may be problematic if the calng-repl reads the generated BMI from clang

in a different target triple.

While the underlying issue is not easy to fix, this patch tries to make

this test green to not bother developers.

Commit: dc5dca1d0118a826459026cfe5819f3f83b599ed

https://github.com/llvm/llvm-project/commit/dc5dca1d0118a826459026cfe5819f3f83b599ed

Author: Chia <sun1011jacobi at gmail.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/RISCV/RISCVISelLowering.cpp

M llvm/test/CodeGen/RISCV/rvv/vector-interleave.ll

A llvm/test/CodeGen/RISCV/rvv/vwadd-mask-sdnode.ll

Log Message:

-----------

[RISCV][Isel] Remove redundant vmerge for the scalable vwadd(u).wv (#80079)

Similar to #78403, but for scalable `vwadd(u).wv`, given that #76785 is recommited.

### Code

```

define <vscale x 8 x i64> @vwadd_wv_mask_v8i32(<vscale x 8 x i32> %x, <vscale x 8 x i64> %y) {

%mask = icmp slt <vscale x 8 x i32> %x, shufflevector (<vscale x 8 x i32> insertelement (<vscale x 8 x i32> poison, i32 42, i64 0), <vscale x 8 x i32> poison, <vscale x 8 x i32> zeroinitializer)

%a = select <vscale x 8 x i1> %mask, <vscale x 8 x i32> %x, <vscale x 8 x i32> zeroinitializer

%sa = sext <vscale x 8 x i32> %a to <vscale x 8 x i64>

%ret = add <vscale x 8 x i64> %sa, %y

ret <vscale x 8 x i64> %ret

}

```

### Before this patch

[Compiler Explorer](https://godbolt.org/z/xsoa5xPrd)

```

vwadd_wv_mask_v8i32:

li a0, 42

vsetvli a1, zero, e32, m4, ta, ma

vmslt.vx v0, v8, a0

vmv.v.i v12, 0

vmerge.vvm v24, v12, v8, v0

vwadd.wv v8, v16, v24

ret

```

### After this patch

```

vwadd_wv_mask_v8i32:

li a0, 42

vsetvli a1, zero, e32, m4, ta, ma

vmslt.vx v0, v8, a0

vsetvli zero, zero, e32, m4, tu, mu

vwadd.wv v16, v16, v8, v0.t

vmv8r.v v8, v16

ret

```

Commit: db49319264d6d2b6f9f7b345495d543210c2cfe3

https://github.com/llvm/llvm-project/commit/db49319264d6d2b6f9f7b345495d543210c2cfe3

Author: Matthias Springer <me at m-sp.org>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M mlir/lib/Dialect/MemRef/IR/MemRefOps.cpp

M mlir/test/Dialect/GPU/decompose-memrefs.mlir

M mlir/test/Dialect/MemRef/fold-memref-alias-ops.mlir

M mlir/test/Dialect/MemRef/invalid.mlir

M mlir/test/Integration/Dialect/SparseTensor/CPU/sparse_rewrite_sort_coo.mlir

Log Message:

-----------

[mlir][memref] `memref.subview`: Verify result strides (#79865)

The `memref.subview` verifier currently checks result shape, element

type, memory space and offset of the result type. However, the strides

of the result type are currently not verified. This commit adds

verification of result strides for non-rank reducing ops and fixes

invalid IR in test cases.

Verification of result strides for ops with rank reductions is more

complex (and there could be multiple possible result types). That is

left for a separate commit.

Also refactor the implementation a bit:

* If `computeMemRefRankReductionMask` could not compute the dropped

dimensions, there must be something wrong with the op. Return

`FailureOr` instead of `std::optional`.

* `isRankReducedMemRefType` did much more than just checking whether the

op has rank reductions or not. Inline the implementation into the

verifier and add better comments.

* `produceSubViewErrorMsg` does not have to be templatized.

Commit: f8525030004f907cd108e7c18df255a6d3b23124

https://github.com/llvm/llvm-project/commit/f8525030004f907cd108e7c18df255a6d3b23124

Author: Jay Foad <jay.foad at amd.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/CodeGen/RegisterClassInfo.cpp

Log Message:

-----------

[CodeGen] Don't include aliases in RegisterClassInfo::IgnoreCSRForAllocOrder (#80015)

Previously we called ignoreCSRForAllocationOrder on every alias of every

CSR which was expensive on targets like AMDGPU which define a very large

number of overlapping register tuples.

On such targets it is simpler and faster to call

ignoreCSRForAllocationOrder once for every physical register.

Differential Revision: https://reviews.llvm.org/D146735

Commit: 96c907dbcebdfbc88f73e097270d171bb83ec3cf

https://github.com/llvm/llvm-project/commit/96c907dbcebdfbc88f73e097270d171bb83ec3cf

Author: Matthias Springer <me at m-sp.org>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M mlir/lib/Dialect/MemRef/IR/MemRefOps.cpp

M mlir/test/Dialect/GPU/decompose-memrefs.mlir

M mlir/test/Dialect/MemRef/fold-memref-alias-ops.mlir

M mlir/test/Dialect/MemRef/invalid.mlir

M mlir/test/Integration/Dialect/SparseTensor/CPU/sparse_rewrite_sort_coo.mlir

Log Message:

-----------

Revert "[mlir][memref] `memref.subview`: Verify result strides" (#80116)

Reverts llvm/llvm-project#79865

I think there is a bug in the stride computation in

`SubViewOp::inferResultType`. (Was already there before this change.)

Reverting this commit for now and updating the original pull request

with a fix and more test cases.

Commit: 64a849a52e08827e889be22ed3ceafe62cd03793

https://github.com/llvm/llvm-project/commit/64a849a52e08827e889be22ed3ceafe62cd03793

Author: Timm Baeder <tbaeder at redhat.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M clang/lib/AST/Interp/ByteCodeEmitter.cpp

M clang/lib/AST/Interp/ByteCodeExprGen.cpp

M clang/lib/AST/Interp/Disasm.cpp

M clang/lib/AST/Interp/IntegralAP.h

M clang/lib/AST/Interp/Interp.h

M clang/lib/AST/Interp/Opcodes.td

M clang/test/AST/Interp/intap.cpp

Log Message:

-----------

[clang][Interp] Support arbitrary precision constants (#79747)

Add (de)serialization support for them, like we do for Floating values.

Commit: d439f3640b6261f372c614afced7bac321af2958

https://github.com/llvm/llvm-project/commit/d439f3640b6261f372c614afced7bac321af2958

Author: jinchen62 <49575973+jinchen62 at users.noreply.github.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M mlir/include/mlir/Dialect/Linalg/TransformOps/LinalgTransformOps.td

M mlir/lib/Dialect/Linalg/TransformOps/LinalgTransformOps.cpp

M mlir/test/Dialect/Linalg/tile-to-forall.mlir

Log Message:

-----------

Add support of param type for transform.structured.tile_using_forall (#72097)

Make transform.structured.tile_using_forall be able to take param type

tile sizes.

Examples:

```

%tile_sizes = transform.param.constant 16 : i64 -> !transform.param<i64>

transform.structured.tile_using_forall %matmul tile_sizes [%tile_sizes : !transform.param<i64>, 32] ( mapping = [#gpu.block<x>, #gpu.block<y>] ) : (!transform.any_op) -> (!transform.any_op, !transform.any_op)

```

```

%c10 = transform.param.constant 10 : i64 -> !transform.any_param

%c20 = transform.param.constant 20 : i64 -> !transform.any_param

%tile_sizes = transform.merge_handles %c10, %c20 : !transform.any_param

transform.structured.tile_using_forall %matmul tile_sizes *(%tile_sizes : !transform.any_param) ( mapping = [#gpu.block<x>, #gpu.block<y>] ) : (!transform.any_op) -> (!transform.any_op, !transform.any_op)

```

Commit: dd736661826e215ac70ff3a4a4ccd75bda0c5ccd

https://github.com/llvm/llvm-project/commit/dd736661826e215ac70ff3a4a4ccd75bda0c5ccd

Author: Sander de Smalen <sander.desmalen at arm.com>

Date: 2024-01-31 (Wed, 31 Jan 2024)

Changed paths:

M llvm/lib/Target/AArch64/AArch64ExpandPseudoInsts.cpp

M llvm/lib/Target/AArch64/AArch64ISelLowering.cpp

M llvm/lib/Target/AArch64/AArch64ISelLowering.h

M llvm/lib/Target/AArch64/AArch64RegisterInfo.cpp

M llvm/lib/Target/AArch64/AArch64SMEInstrInfo.td

M llvm/test/CodeGen/AArch64/sme-disable-gisel-fisel.ll

A llvm/test/CodeGen/AArch64/sme-pstate-sm-changing-call-disable-coalescing.ll

M llvm/test/CodeGen/AArch64/sme-streaming-body.ll

M llvm/test/CodeGen/AArch64/sme-streaming-compatible-interface.ll

M llvm/test/CodeGen/AArch64/sme-streaming-interface.ll

M llvm/test/CodeGen/AArch64/sme-streaming-mode-changing-call-disable-stackslot-scavenging.ll

Log Message:

-----------

[SME] Stop RA from coalescing COPY instructions that transcend beyond smstart/smstop. (#78294)

This patch introduces a 'COALESCER_BARRIER' which is a pseudo node that

expands to