[all-commits] [llvm/llvm-project] 586986: [Flang] Add multiline error message support to pas...

Justin Bogner via All-commits

all-commits at lists.llvm.org

Thu Nov 30 09:46:33 PST 2023

Branch: refs/heads/users/bogner/spr/clangsema-dont-say-is-declared-here-for-invalid-template-locations

Home: https://github.com/llvm/llvm-project

Commit: 586986a063ee4b9a7490aac102e103bab121c764

https://github.com/llvm/llvm-project/commit/586986a063ee4b9a7490aac102e103bab121c764

Author: madanial0 <118996571+madanial0 at users.noreply.github.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M flang/test/Driver/pass-plugin-not-found.f90

Log Message:

-----------

[Flang] Add multiline error message support to pass-plugin-not-found (NFC) (#73601)

The error message above has multiple lines on AIX, adding

`{{[[:space:]].*}}` to match multiple lines

Co-authored-by: Mark Danial <mark.danial at ibm.com>

Commit: c0b926939829d9d4bb6ac5825e62f30960b6ed22

https://github.com/llvm/llvm-project/commit/c0b926939829d9d4bb6ac5825e62f30960b6ed22

Author: Luke Lau <luke at igalia.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/RISCV/RISCVInsertVSETVLI.cpp

Log Message:

-----------

[RISCV] Add helper to copy the AVL of another VSETVLIInfo. NFC

Commit: 8a66510fa73c1507c2a58338e180ddb075993a5a

https://github.com/llvm/llvm-project/commit/8a66510fa73c1507c2a58338e180ddb075993a5a

Author: Pierre van Houtryve <pierre.vanhoutryve at amd.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/IR/IntrinsicsAMDGPU.td

M llvm/lib/Target/AMDGPU/AMDGPUCodeGenPrepare.cpp

M llvm/lib/Target/AMDGPU/AMDGPUInstrInfo.td

M llvm/lib/Target/AMDGPU/VOP2Instructions.td

M llvm/test/CodeGen/AMDGPU/amdgpu-codegenprepare-mul24.ll

M llvm/test/CodeGen/AMDGPU/machine-sink-temporal-divergence-swdev407790.ll

M llvm/test/CodeGen/AMDGPU/mul_int24.ll

M llvm/test/CodeGen/AMDGPU/mul_uint24-amdgcn.ll

Log Message:

-----------

[AMDGPU] Don't create mulhi_24 in CGP (#72983)

Instead, create a mul24 with a 64 bit result and let ISel take care of

it.

This allows patterns to simply match mul24 even for 64-bit muls instead of having to match both mul/mulhi and a buildvector/bitconvert/etc.

Commit: 030047c432cac133738be68fa0974f70e69dd58d

https://github.com/llvm/llvm-project/commit/030047c432cac133738be68fa0974f70e69dd58d

Author: cor3ntin <corentinjabot at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/docs/ReleaseNotes.rst

M clang/include/clang/Sema/ExternalSemaSource.h

M clang/include/clang/Sema/MultiplexExternalSemaSource.h

M clang/include/clang/Sema/Sema.h

M clang/include/clang/Serialization/ASTBitCodes.h

M clang/include/clang/Serialization/ASTReader.h

M clang/lib/Sema/MultiplexExternalSemaSource.cpp

M clang/lib/Sema/SemaDecl.cpp

M clang/lib/Sema/SemaExpr.cpp

M clang/lib/Sema/SemaTemplateInstantiateDecl.cpp

M clang/lib/Serialization/ASTReader.cpp

M clang/lib/Serialization/ASTWriter.cpp

A clang/test/PCH/instantiate-used-constexpr-function.cpp

A clang/test/SemaTemplate/instantiate-used-constexpr-function.cpp

Log Message:

-----------

[Clang] Eagerly instantiate used constexpr function upon definition. (#73463)

Despite CWG2497 not being resolved, it is reasonable to expect the

following code to compile (and which is supported by other compilers)

```cpp

template<typename T> constexpr T f();

constexpr int g() { return f<int>(); } // #1

template<typename T> constexpr T f() { return 123; }

int k[g()];

// #2

```

To that end, we eagerly instantiate all referenced specializations of

constexpr functions when they are defined.

We maintain a map of (pattern, [instantiations]) independent of

`PendingInstantiations` to avoid having to iterate that list after each

function definition.

We should apply the same logic to constexpr variables, but I wanted to

keep the PR small.

Fixes #73232

Commit: 5891a8f7ce0a7b866a5bc06c34092fbdb28dda1c

https://github.com/llvm/llvm-project/commit/5891a8f7ce0a7b866a5bc06c34092fbdb28dda1c

Author: Jie Fu <jiefu at tencent.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/Sema/MultiplexExternalSemaSource.cpp

Log Message:

-----------

[clang] Remove extra ';' in MultiplexExternalSemaSource.cpp (NFC)

/llvm-project/clang/lib/Sema/MultiplexExternalSemaSource.cpp:317:2:

error: extra ';' outside of a function is incompatible with C++98 [-Werror,-Wc++98-compat-extra-semi]

};

^

1 error generated.

Commit: 511ba45a47d6f9e48ad364181830c9fb974135b2

https://github.com/llvm/llvm-project/commit/511ba45a47d6f9e48ad364181830c9fb974135b2

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/MCTargetDesc/X86InstPrinterCommon.cpp

M llvm/lib/Target/X86/X86DomainReassignment.cpp

M llvm/lib/Target/X86/X86ExpandPseudo.cpp

M llvm/lib/Target/X86/X86InstrAVX512.td

M llvm/lib/Target/X86/X86InstrInfo.cpp

M llvm/lib/Target/X86/X86InstrInfo.td

A llvm/test/CodeGen/X86/apx/kmov-copy-to-from-asymmetric-reg.ll

A llvm/test/CodeGen/X86/apx/kmov-domain-assignment.ll

A llvm/test/CodeGen/X86/apx/kmov-isel.ll

A llvm/test/CodeGen/X86/apx/kmov-postrapseudos.ll

A llvm/test/MC/Disassembler/X86/apx/kmov.txt

A llvm/test/MC/X86/apx/kmov-att.s

A llvm/test/MC/X86/apx/kmov-intel.s

M llvm/test/TableGen/x86-fold-tables.inc

Log Message:

-----------

[X86][MC][CodeGen] Support EGPR for KMOV (#73781)

KMOV is essential for copy between k-registers and GPRs.

R16-R31 was added into GPRs in #70958, so we extend KMOV for these new

registers first.

This patch

1. Promotes KMOV instructions from VEX space to EVEX space

2. Emits prefix {evex} for the EVEX variants

3. Prefers EVEX variant than VEX variant in ISEL and optimizations for

better RA

EVEX variants will be compressed to VEX variants by existing EVEX2VEX

pass if no EGPR is used.

RFC:

https://discourse.llvm.org/t/rfc-design-for-apx-feature-egpr-and-ndd-support/73031/4

TAG: llvm-test-suite && CPU2017 can be built with feature egpr

successfully.

Commit: f1fba63f1282a21e6adc5f7732e8583c52792744

https://github.com/llvm/llvm-project/commit/f1fba63f1282a21e6adc5f7732e8583c52792744

Author: Rik Huijzer <github at huijzer.xyz>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/docs/Dialects/Vector.md

Log Message:

-----------

[mlir][vector][doc] 0D vectors (#73792)

Currently, the only mention of 0d vectors in the MLIR source code that I

could find was:

> 0D vectors are allowed by omitting the dimension: `vector<f32>`.

in

[`BuiltinTypes.td`](https://github.com/llvm/llvm-project/blob/437a48b2d9bfc6e38a0ca43f1cee48ceaf0fe249/mlir/include/mlir/IR/BuiltinTypes.td#L1046-L1047).

This patch adds a summary of

https://discourse.llvm.org/t/what-is-the-semantics-of-memref-0xf32-and-tensor-0xf32/3557

and https://discourse.llvm.org/t/should-we-have-0-d-vectors/3097/5.

Commit: ae3cd2d04a88937881ac1f9c5d34f0e0cf96d5bc

https://github.com/llvm/llvm-project/commit/ae3cd2d04a88937881ac1f9c5d34f0e0cf96d5bc

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/Support/X86FoldTablesUtils.h

Log Message:

-----------

[X86][NFC] Clang-format X86FoldTablesUtils.h

Commit: ae6eedd27556c32232f4e8be1292ffa0e1f16d90

https://github.com/llvm/llvm-project/commit/ae6eedd27556c32232f4e8be1292ffa0e1f16d90

Author: Rik Huijzer <github at huijzer.xyz>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/test/Dialect/Affine/value-bounds-op-interface-impl.mlir

M mlir/test/Dialect/NVGPU/transform-pipeline-shared.mlir

Log Message:

-----------

[mlir] Fix two `CHECK:` typos (#73803)

Out of curiosity, I ran [typos](https://github.com/crate-ci/typos)

against MLIR. It found two `CHECK:` typos (and many minor typos; which

I'm not gonna work on today).

Commit: 6d2dfd37bd50b21ed90427052198bd1f06c761f8

https://github.com/llvm/llvm-project/commit/6d2dfd37bd50b21ed90427052198bd1f06c761f8

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/Scalar/LoopPassManager.cpp

M llvm/test/Other/loop-mssa-not-preserved.ll

Log Message:

-----------

[LPM] Set gen_crash_diag=false for non-MSSA pass in MSSA pipeline

When a loop pass that does not preserve MSSA is run as part of a

loop-mssa pipeline, this is user error and we should not ask for

a bug report.

Fixes https://github.com/llvm/llvm-project/issues/73554.

Commit: b72456120f1db38ed7068fb592fcf768c6d5cce2

https://github.com/llvm/llvm-project/commit/b72456120f1db38ed7068fb592fcf768c6d5cce2

Author: wanglei <wanglei at loongson.cn>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/LoongArch/LoongArchISelLowering.cpp

M llvm/lib/Target/LoongArch/LoongArchInstrInfo.cpp

M llvm/lib/Target/LoongArch/LoongArchLASXInstrInfo.td

M llvm/lib/Target/LoongArch/LoongArchLSXInstrInfo.td

A llvm/test/CodeGen/LoongArch/lasx/ir-instruction/extractelement.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/extractelement.ll

Log Message:

-----------

[LoongArch] Add codegen support for extractelement (#73759)

Add codegen support for extractelement when enable `lsx` or `lasx`

feature.

Commit: e9869b57707fc6dd828872a70c2f377cc0061978

https://github.com/llvm/llvm-project/commit/e9869b57707fc6dd828872a70c2f377cc0061978

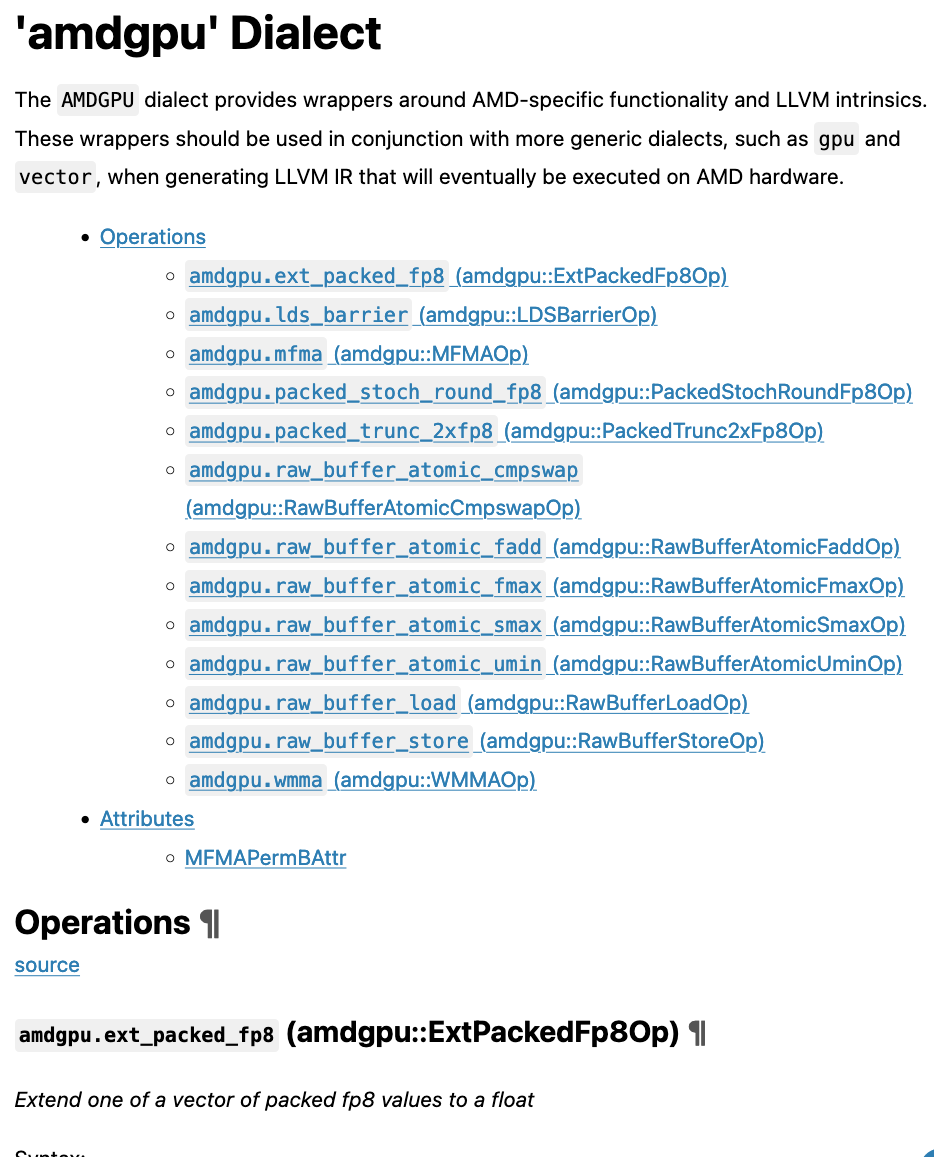

Author: Rik Huijzer <github at huijzer.xyz>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/test/mlir-tblgen/gen-dialect-doc.td

M mlir/tools/mlir-tblgen/OpDocGen.cpp

Log Message:

-----------

[mlir][docgen] Add ops source link (#73657)

This patch suggests to change two things. Firstly, it adds a source link

above the generated operations docs (above the `emitOpDoc` calls). This

link will point directly to the source TableGen file for the group of

operations. For example, for the current

[`amdgpu`](https://mlir.llvm.org/docs/Dialects/AMDGPU/) page, the link

will add a source link below the "Operation definition" heading pointing

to

[`mlir/include/mlir/Dialect/AMDGPU/IR/AMDGPU.td`](https://github.com/llvm/llvm-project/blob/main/mlir/include/mlir/Dialect/AMDGPU/IR/AMDGPU.td).

The link is wrapped in a "op-definitions-source-link" class which could

allow for custom styling, but it also looks reasonable without custom

styling I think:

Secondly, this patch simplifies the header names such as "Operation

definition" and "Attribute definition" to "Operations" and "Attributes"

respectively. This is in line with manually defined subheadings on pages

such as the one for the

[`vector`](https://mlir.llvm.org/docs/Dialects/Vector/#operations)

dialect.

Commit: 14ca8d44d0f44ea5125b3c41b66276c902929a54

https://github.com/llvm/llvm-project/commit/14ca8d44d0f44ea5125b3c41b66276c902929a54

Author: Mariya Podchishchaeva <mariya.podchishchaeva at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/docs/ReleaseNotes.rst

M clang/lib/Sema/SemaDecl.cpp

M clang/test/SemaTemplate/dependent-base-classes.cpp

Log Message:

-----------

[clang] Fix a bug with qualified name lookup into current instantiation (#73018)

Due to d0d2ee0e4bbe915d649e983c12d37bcfcf58823c clang doesn't perform

qualified name lookup into the current instantiation when it has

dependent bases, because of that `getTypeName` call always returns null

for unknown specialization case. When there is a `typename` keyword,

`DependentNameType` is constructed instead of simply returning null.

This change attempts to do the same in case of `typename` absence.

Fixes https://github.com/llvm/llvm-project/issues/13826

Commit: eb64697a7b75d2b22041cc992fad0c8dfa7989cb

https://github.com/llvm/llvm-project/commit/eb64697a7b75d2b22041cc992fad0c8dfa7989cb

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86InstrAVX512.td

M llvm/test/CodeGen/X86/avx512vlvp2intersect-intrinsics.ll

M llvm/test/CodeGen/X86/avx512vp2intersect-intrinsics.ll

M llvm/test/CodeGen/X86/stack-folding-avx512vp2intersect.ll

M llvm/test/CodeGen/X86/vp2intersect_multiple_pairs.ll

Log Message:

-----------

[X86][Codegen] Correct the domain of VP2INTERSECT

GenericDomain -> SSEPackedInt

Found by #73654

Commit: 9d4c3e90356f968781ea3fe3c38b011d13d95c59

https://github.com/llvm/llvm-project/commit/9d4c3e90356f968781ea3fe3c38b011d13d95c59

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86ISelLowering.cpp

M llvm/test/CodeGen/X86/vec_fneg.ll

Log Message:

-----------

[X86] Enable v8f16 FNEG custom lowering

Commit: abc60e9808820c3f6614e6815909d43ed085460e

https://github.com/llvm/llvm-project/commit/abc60e9808820c3f6614e6815909d43ed085460e

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/CodeGen/X86/vec_fabs.ll

Log Message:

-----------

[X86] vec_fabs.ll - add SSE test coverage

Commit: 06b9d92e0e6536d460db3bef6a55de0ecd244927

https://github.com/llvm/llvm-project/commit/06b9d92e0e6536d460db3bef6a55de0ecd244927

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86ISelLowering.cpp

M llvm/test/CodeGen/X86/vec_fabs.ll

Log Message:

-----------

[X86] Enable v8f16 FABS custom lowering on SSE2 targets

Commit: 8851e411edd5990d886d171568d97454258b06d3

https://github.com/llvm/llvm-project/commit/8851e411edd5990d886d171568d97454258b06d3

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86ISelLowering.cpp

M llvm/test/CodeGen/X86/vec_fneg.ll

Log Message:

-----------

[X86] Enable v16f16 FNEG custom lowering on AVX targets

Commit: d2856ff457ca0563f42ce9a12d7c7537b7234f3a

https://github.com/llvm/llvm-project/commit/d2856ff457ca0563f42ce9a12d7c7537b7234f3a

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86ISelLowering.cpp

M llvm/test/CodeGen/X86/vec_fneg.ll

Log Message:

-----------

[X86] Enable v32f16 FNEG custom lowering on AVX512 targets

Commit: 3246a32d3f6b97467ecdf2682d44a6515dbccf96

https://github.com/llvm/llvm-project/commit/3246a32d3f6b97467ecdf2682d44a6515dbccf96

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/Scalar/LoopStrengthReduce.cpp

Log Message:

-----------

Fix MSVC "not all control paths return a value" warning. NFC.

Commit: eef8e1d206dc01c081a0ca29b7f9e0c39d33446e

https://github.com/llvm/llvm-project/commit/eef8e1d206dc01c081a0ca29b7f9e0c39d33446e

Author: Lucas Duarte Prates <lucas.prates at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/test/Driver/aarch64-v95a.c

M llvm/include/llvm/TargetParser/AArch64TargetParser.h

M llvm/lib/Target/AArch64/AArch64.td

M llvm/lib/Target/AArch64/AArch64InstrFormats.td

M llvm/lib/Target/AArch64/AArch64InstrInfo.td

M llvm/lib/Target/AArch64/AArch64SVEInstrInfo.td

M llvm/lib/Target/AArch64/AArch64SchedA64FX.td

M llvm/lib/Target/AArch64/AArch64SchedNeoverseN2.td

M llvm/lib/Target/AArch64/AArch64SchedNeoverseV1.td

M llvm/lib/Target/AArch64/AArch64SchedNeoverseV2.td

M llvm/lib/Target/AArch64/AsmParser/AArch64AsmParser.cpp

M llvm/lib/Target/AArch64/SVEInstrFormats.td

A llvm/test/MC/AArch64/SVE/armv9.5a-cpa.s

A llvm/test/MC/AArch64/armv9.5a-cpa.s

M llvm/test/MC/AArch64/basic-a64-diagnostics.s

M llvm/test/MC/AArch64/basic-a64-instructions.s

A llvm/test/MC/Disassembler/AArch64/armv9.5a-cpa.txt

M llvm/test/MC/Disassembler/AArch64/basic-a64-instructions.txt

M llvm/unittests/TargetParser/TargetParserTest.cpp

Log Message:

-----------

[AArch64] Assembly support for the Checked Pointer Arithmetic Extension (#73777)

This introduces assembly support for the Checked Pointer Arithmetic

Extension (FEAT_CPA), annouced as part of the Armv9.5-A architecture

version.

The changes include:

* New subtarget feature for FEAT_CPA

* New scalar instruction for pointer arithmetic

* ADDPT, SUBPT, MADDPT, and MSUBPT

* New SVE instructions for pointer arithmetic

* ADDPT (vectors, predicated), ADDPT (vectors, unpredicated)

* SUBPT (vectors, predicated), SUBPT (vectors, unpredicated)

* MADPT and MLAPT

* New ID_AA64ISAR3_EL1 system register

Mode details about the extension can be found at:

* https://community.arm.com/arm-community-blogs/b/architectures-and-processors-blog/posts/arm-a-profile-architecture-developments-2023

* https://developer.arm.com/documentation/ddi0602/2023-09/

Co-authored-by: Rodolfo Wottrich <rodolfo.wottrich at arm.com>

Commit: b04a419be1cac5711029b511cfe16e6748a44a4d

https://github.com/llvm/llvm-project/commit/b04a419be1cac5711029b511cfe16e6748a44a4d

Author: Jonas Paulsson <paulson1 at linux.ibm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/AST/ASTContext.cpp

Log Message:

-----------

Minor refactororing of ASTContext::getDeclAlign() (NFC) (#72977)

Commit: eaff02f28e194b497ec2d9a6bbecc33b54f6df27

https://github.com/llvm/llvm-project/commit/eaff02f28e194b497ec2d9a6bbecc33b54f6df27

Author: Benjamin Maxwell <benjamin.maxwell at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/include/mlir/Dialect/ArmSME/IR/ArmSME.h

A mlir/include/mlir/Dialect/ArmSME/IR/ArmSMEEnums.h

M mlir/include/mlir/Dialect/ArmSME/IR/ArmSMEIntrinsicOps.td

M mlir/include/mlir/Dialect/ArmSME/IR/ArmSMEOps.td

M mlir/include/mlir/Dialect/ArmSME/IR/CMakeLists.txt

M mlir/include/mlir/Dialect/ArmSME/Transforms/Passes.h

M mlir/include/mlir/Dialect/ArmSME/Utils/Utils.h

M mlir/lib/Conversion/ArmSMEToLLVM/ArmSMEToLLVM.cpp

M mlir/lib/Conversion/ArmSMEToLLVM/CMakeLists.txt

M mlir/lib/Conversion/ArmSMEToSCF/ArmSMEToSCF.cpp

M mlir/lib/Conversion/ArmSMEToSCF/CMakeLists.txt

M mlir/lib/Conversion/VectorToArmSME/CMakeLists.txt

M mlir/lib/Conversion/VectorToArmSME/VectorToArmSME.cpp

M mlir/lib/Dialect/ArmSME/CMakeLists.txt

M mlir/lib/Dialect/ArmSME/IR/ArmSME.cpp

M mlir/lib/Dialect/ArmSME/IR/CMakeLists.txt

A mlir/lib/Dialect/ArmSME/IR/Utils.cpp

M mlir/lib/Dialect/ArmSME/Transforms/CMakeLists.txt

M mlir/lib/Dialect/ArmSME/Transforms/TileAllocation.cpp

R mlir/lib/Dialect/ArmSME/Utils/CMakeLists.txt

R mlir/lib/Dialect/ArmSME/Utils/Utils.cpp

M mlir/test/Conversion/ArmSMEToSCF/arm-sme-to-scf.mlir

M mlir/test/Dialect/ArmSME/arith-ops-to-sme.mlir

R mlir/test/Dialect/ArmSME/arm-sme-to-llvm-casts.mlir

M mlir/test/Dialect/ArmSME/arm-sme-to-llvm.mlir

M mlir/test/Dialect/ArmSME/canonicalize.mlir

M mlir/test/Dialect/ArmSME/cse.mlir

M mlir/test/Dialect/ArmSME/invalid.mlir

M mlir/test/Dialect/ArmSME/roundtrip.mlir

A mlir/test/Dialect/ArmSME/tile-allocation-invalid.mlir

M mlir/test/Dialect/ArmSME/tile-allocation.mlir

M mlir/test/Dialect/ArmSME/tile-zero-masks.mlir

M mlir/test/Dialect/ArmSME/vector-ops-to-llvm.mlir

M mlir/test/Dialect/ArmSME/vector-ops-to-sme.mlir

M mlir/test/Integration/Dialect/Linalg/CPU/ArmSME/fill-2d.mlir

M mlir/test/Integration/Dialect/Linalg/CPU/ArmSME/matmul-transpose-a.mlir

M mlir/test/Integration/Dialect/Linalg/CPU/ArmSME/matmul.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-load-vertical.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-outerproduct-f32.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-outerproduct-f64.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-transfer-read-2d.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-transfer-write-2d.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/test-transpose.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/tile_fill.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/vector-load-store.mlir

M mlir/test/Integration/Dialect/Vector/CPU/ArmSME/vector-ops.mlir

M mlir/test/Target/LLVMIR/arm-sme-invalid.mlir

M mlir/test/Target/LLVMIR/arm-sme.mlir

Log Message:

-----------

[mlir][ArmSME] Switch to an attribute-based tile allocation scheme (#73253)

This reworks the ArmSME dialect to use attributes for tile allocation.

This has a number of advantages and corrects some issues with the

previous approach:

* Tile allocation can now be done ASAP (i.e. immediately after

`-convert-vector-to-arm-sme`)

* SSA form for control flow is now supported (e.g.`scf.for` loops that

yield tiles)

* ArmSME ops can be converted to intrinsics very late (i.e. after

lowering to control flow)

* Tests are simplified by removing constants and casts

* Avoids correctness issues with representing LLVM `immargs` as MLIR

values

- The tile ID on the SME intrinsics is an `immarg` (so is required to be

a compile-time constant), `immargs` should be mapped to MLIR attributes

(this is already the case for intrinsics in the LLVM dialect)

- Using MLIR values for `immargs` can lead to invalid LLVM IR being

generated (and passes such as -cse making incorrect optimizations)

As part of this patch we bid farewell to the following operations:

```mlir

arm_sme.get_tile_id : i32

arm_sme.cast_tile_to_vector : i32 to vector<[4]x[4]xi32>

arm_sme.cast_vector_to_tile : vector<[4]x[4]xi32> to i32

```

These are now replaced with:

```mlir

// Allocates a new tile with (indeterminate) state:

arm_sme.get_tile : vector<[4]x[4]xi32>

// A placeholder operation for lowering ArmSME ops to intrinsics:

arm_sme.materialize_ssa_tile : vector<[4]x[4]xi32>

```

The new tile allocation works by operations implementing the

`ArmSMETileOpInterface`. This interface says that an operation needs to

be assigned a tile ID, and may conditionally allocate a new SME tile.

Operations allocate a new tile by implementing...

```c++

std::optional<arm_sme::ArmSMETileType> getAllocatedTileType()

```

...and returning what type of tile the op allocates (ZAB, ZAH, etc).

Operations that don't allocate a tile return `std::nullopt` (which is

the default behaviour).

Currently the following ops are defined as allocating:

```mlir

arm_sme.get_tile

arm_sme.zero

arm_sme.tile_load

arm_sme.outerproduct // (if no accumulator is specified)

```

Allocating operations become the roots for the tile allocation pass,

which currently just (naively) assigns all transitive uses of a root

operation the same tile ID. However, this is enough to handle current

use cases.

Once tile IDs have been allocated subsequent rewrites can forward the

tile IDs to any newly created operations.

Commit: 0817efc4767bbfea282ad82d6517454288a1d59b

https://github.com/llvm/llvm-project/commit/0817efc4767bbfea282ad82d6517454288a1d59b

Author: Kohei Yamaguchi <fix7211 at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/docs/Dialects/Transform.md

M mlir/docs/Passes.md

Log Message:

-----------

[mlir][docs] Add missing .md into Transform and Passes docs(NFC) (#73916)

Fix broken docs for MeshDialect's pass and Transform dialect's loop

extension.

Commit: e620035a28d5d957623aa7b4aeda35ab5130e2c9

https://github.com/llvm/llvm-project/commit/e620035a28d5d957623aa7b4aeda35ab5130e2c9

Author: Serge Pavlov <sepavloff at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/AST/ExprConstant.cpp

M clang/test/SemaCXX/rounding-math.cpp

Log Message:

-----------

[clang] Use current rounding mode for float inc/dec (#73770)

Increment and decrement are equivalent to adding or subtracting 1. For

the floating-point values these operations depend on the current

rounding mode. Teach constant evaluator to perform ++ and -- according

to the current floating-point environment.

Pull request: https://github.com/llvm/llvm-project/pull/73770

Commit: 53a24c33f09b81b8f009afbabd05f7086db3f288

https://github.com/llvm/llvm-project/commit/53a24c33f09b81b8f009afbabd05f7086db3f288

Author: Michael Buch <michaelbuch12 at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/CodeGen/CGDebugInfo.cpp

M clang/test/CodeGenCXX/debug-info-static-inline-member.cpp

M clang/test/CodeGenCXX/debug-info-static-member.cpp

Log Message:

-----------

[clang][DebugInfo] Improve heuristic to determine whether to evaluate a static variable's initializer (#72974)

This patch extracts the logic to evaluate a C++ static data-member's

constant initializer. This logic will be re-used in an upcoming patch.

It also makes the check for whether we are dealing with a constant

initializer more robust/idiomatic, which revealed a bug in the

`debug-info-static-inline-member` test (which existed since its

introduction in https://github.com/llvm/llvm-project/pull/71780)

**Test changes**

* `debug-info-static-member.cpp`:

* We added the check for `const_b` as part of the

patch series in `638a8393615e911b729d5662096f60ef49f1c65e`.

The check for `isUsableAsConstantExpression` added in the current patch

doesn't support constant inline floats (since they are neither constexpr

nor

integrals). This isn't a regression since before said patch series

we wouldn't ever emit the definition for `const_b` anyway. Now

we just don't do it for `inline const float`s. This is consistent with

GCC's behaviour starting with C++11.

* `debug-info-static-inline-member`:

* This was just a bug which is now fixed. We shouldn't emit

a `DW_AT_const_value` for a non-const static.

Commit: e78a45dd104c25475dcf141e0146790e9f2a219c

https://github.com/llvm/llvm-project/commit/e78a45dd104c25475dcf141e0146790e9f2a219c

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/utils/TableGen/X86FoldTablesEmitter.cpp

Log Message:

-----------

[X86][NFC] Refine code in X86FoldTablesEmitter.cpp

Split NFC in #73654 into a seperate commit.

Commit: 7d5f79f13b498ba19ae257d75a726e354a076ed9

https://github.com/llvm/llvm-project/commit/7d5f79f13b498ba19ae257d75a726e354a076ed9

Author: Antonio Frighetto <me at antoniofrighetto.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineAddSub.cpp

M llvm/test/Transforms/InstCombine/add.ll

Log Message:

-----------

[InstCombine] Handle equality comparison when flooring by constant 2

Support `icmp eq` when reducing signed divisions by power of 2 to

arithmetic shift right, as `icmp ugt` may have been canonicalized

into `icmp eq` by the time additions are folded into `ashr`.

Fixes: https://github.com/llvm/llvm-project/issues/73622.

Proof: https://alive2.llvm.org/ce/z/8-eUdb.

Commit: c80b91bce3a5a92281ad1c7e090ac25e7a5bd395

https://github.com/llvm/llvm-project/commit/c80b91bce3a5a92281ad1c7e090ac25e7a5bd395

Author: Michael Buch <michaelbuch12 at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/test/CodeGenCXX/debug-info-static-inline-member.cpp

Log Message:

-----------

[clang][DebugInfo][test] Remove unchecked member variable in debug-info-static-inline-member

The check for this was removed in

https://github.com/llvm/llvm-project/pull/72974

This patch removes the member from the source itself since

it was confusing FileCheck

Commit: 092507a730fa4fad6dbe544cd139cfb7e8179aa4

https://github.com/llvm/llvm-project/commit/092507a730fa4fad6dbe544cd139cfb7e8179aa4

Author: Momchil Velikov <momchil.velikov at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/CodeGen/CodeGenModule.cpp

M clang/lib/Driver/ToolChains/Clang.cpp

M clang/test/CodeGen/stack-clash-protection.c

Log Message:

-----------

[clang][AArch64] Pass down stack clash protection options to LLVM/Backend (#68993)

Commit: 4793bce709018cf44015575a4466fcc634f70556

https://github.com/llvm/llvm-project/commit/4793bce709018cf44015575a4466fcc634f70556

Author: Jean Perier <jperier at nvidia.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M flang/lib/Lower/ConvertCall.cpp

M flang/lib/Optimizer/Builder/HLFIRTools.cpp

M flang/lib/Optimizer/HLFIR/Transforms/BufferizeHLFIR.cpp

Log Message:

-----------

[flang] Remove useless ConvertExpr.h includes in Optimizer

Added by mistake in https://github.com/llvm/llvm-project/pull/73658.

Not needed and breaks shared library builds.

Commit: e653e0303db024fe817e17c70c9d6d75ab9605b9

https://github.com/llvm/llvm-project/commit/e653e0303db024fe817e17c70c9d6d75ab9605b9

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

A llvm/test/CodeGen/X86/vec_fcopysign.ll

Log Message:

-----------

[X86] Add fcopysign vector test coverage

Commit: 1d20b009a0e274c0db518b0bca0dd5daabcc8754

https://github.com/llvm/llvm-project/commit/1d20b009a0e274c0db518b0bca0dd5daabcc8754

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86ISelLowering.cpp

M llvm/test/CodeGen/X86/vec_fcopysign.ll

Log Message:

-----------

[X86] Enable v8f16/v16f16/v32f16 FCOPYSIGN custom lowering on SSE2/AVX/AVX512 targets

Commit: 00a10efdb12dbc3f5a0ba16f6c92cac713f0590b

https://github.com/llvm/llvm-project/commit/00a10efdb12dbc3f5a0ba16f6c92cac713f0590b

Author: Antonio Frighetto <me at antoniofrighetto.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/Transforms/InstCombine/add3.ll

M llvm/test/Transforms/InstCombine/addnegneg.ll

M llvm/test/Transforms/InstCombine/allocsize.ll

Log Message:

-----------

[InstCombine] Regenerate test checks (NFC)

Commit: 4db451a87d56ab469af2eecbae47338e540b1276

https://github.com/llvm/llvm-project/commit/4db451a87d56ab469af2eecbae47338e540b1276

Author: Paul Walker <paul.walker at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/AArch64/AArch64ISelLowering.cpp

M llvm/lib/Target/AArch64/AArch64ISelLowering.h

A llvm/test/CodeGen/AArch64/sve-fixed-length-function-calls.ll

A llvm/test/CodeGen/AArch64/sve-fixed-length-functions.ll

Log Message:

-----------

[LLVM][SVE] Honour calling convention when using SVE for fixed length vectors. (#70847)

NOTE: I'm not sure how many of the corner cases are part of the

documented ABI but that shouldn't matter because my goal is for

`-msve-vector-bits` to have no affect on the way arguments and returns

are processed.

Commit: 269e3049eab3b8c6c22addee3b72199fdad56d07

https://github.com/llvm/llvm-project/commit/269e3049eab3b8c6c22addee3b72199fdad56d07

Author: David Green <david.green at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/CodeGen/AArch64/sme-aarch64-svcount.ll

Log Message:

-----------

[AArch64] Remove invalid check lines from sme-aarch64-svcount.ll. NFC

Commit: 2425e2940eb4f24de296ada92e25d6aad9578cd0

https://github.com/llvm/llvm-project/commit/2425e2940eb4f24de296ada92e25d6aad9578cd0

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/IR/IRBuilder.h

M llvm/include/llvm/IR/Instruction.h

M llvm/lib/IR/Instruction.cpp

M llvm/lib/Transforms/Coroutines/CoroFrame.cpp

M llvm/lib/Transforms/InstCombine/InstCombineAndOrXor.cpp

M llvm/lib/Transforms/InstCombine/InstCombineCalls.cpp

M llvm/lib/Transforms/InstCombine/InstructionCombining.cpp

M llvm/lib/Transforms/Scalar/GuardWidening.cpp

M llvm/lib/Transforms/Scalar/LoopIdiomRecognize.cpp

M llvm/lib/Transforms/Scalar/Reassociate.cpp

M llvm/lib/Transforms/Vectorize/VectorCombine.cpp

Log Message:

-----------

[DebugInfo][RemoveDIs] Have getInsertionPtAfterDef return an iterator (#73149)

Part of the "RemoveDIs" project to remove debug intrinsics requires

passing block-positions around in iterators rather than as instruction

pointers, allowing some debug-info to reside in BasicBlock::iterator.

This means getInsertionPointAfterDef has to return an iterator, and as

it can return no-instruction that means returning an optional iterator.

This patch changes the signature for getInsertionPtAfterDef and then

patches up the various places that use it to handle the different type.

This would overall be an NFC patch, however in

InstCombinerImpl::freezeOtherUses I've started skipping any debug

intrinsics at the returned insert-position. This should not have any

_meaningful_ effect on the compiler output: at worst it means variable

assignments that are skipped will now cover the freeze instruction and

anything inserted before it, which should be inconsequential.

Sadly: this makes the function signature ugly. This is probably the

ugliest piece of fallout for the "RemoveDIs" work, but it serves the

overall purpose of improving compile times and not allowing `-g` to

affect compiler output, so should be worthwhile in the end.

Commit: c84061fd343cdd647dd18321aa555c5d358c2d65

https://github.com/llvm/llvm-project/commit/c84061fd343cdd647dd18321aa555c5d358c2d65

Author: Rik Huijzer <github at huijzer.xyz>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/lib/Conversion/VectorToSCF/VectorToSCF.cpp

M mlir/test/Conversion/VectorToSCF/vector-to-scf.mlir

Log Message:

-----------

[mlir][vector] Fix a `target-rank=0` unrolling (#73365)

Fixes https://github.com/llvm/llvm-project/issues/64269.

With this patch, calling `mlir-opt "-convert-vector-to-scf=full-unroll

target-rank=0"` on

```mlir

func.func @main(%vec : vector<2xi32>) {

%alloc = memref.alloc() : memref<4xi32>

%c0 = arith.constant 0 : index

vector.transfer_write %vec, %alloc[%c0] : vector<2xi32>, memref<4xi32>

return

}

```

will result in

```mlir

module {

func.func @main(%arg0: vector<2xi32>) {

%c0 = arith.constant 0 : index

%c1 = arith.constant 1 : index

%alloc = memref.alloc() : memref<4xi32>

%0 = vector.extract %arg0[0] : i32 from vector<2xi32>

%1 = vector.broadcast %0 : i32 to vector<i32>

vector.transfer_write %1, %alloc[%c0] : vector<i32>, memref<4xi32>

%2 = vector.extract %arg0[1] : i32 from vector<2xi32>

%3 = vector.broadcast %2 : i32 to vector<i32>

vector.transfer_write %3, %alloc[%c1] : vector<i32>, memref<4xi32>

return

}

}

```

I've also tried to proactively find other `target-rank=0` bugs, but

couldn't find any. `options.targetRank` is only used 8 times throughout

the `mlir` folder, all inside `VectorToSCF.cpp`. None of the other uses

look like they could cause a crash. I've also tried

```mlir

func.func @main(%vec : vector<2xi32>) -> vector<2xi32> {

%alloc = memref.alloc() : memref<4xindex>

%c0 = arith.constant 0 : index

%out = vector.transfer_read %alloc[%c0], %c0 : memref<4xindex>, vector<2xi32>

return %out : vector<2xi32>

}

```

with `"--convert-vector-to-scf=full-unroll target-rank=0"` and that also

didn't crash. (Maybe obvious. I have to admit that I'm not very familiar

with these ops.)

Commit: b9b37ea9493b5c1cadaf9cc8547a4525a6ab3854

https://github.com/llvm/llvm-project/commit/b9b37ea9493b5c1cadaf9cc8547a4525a6ab3854

Author: Mariya Podchishchaeva <mariya.podchishchaeva at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/Sema/SemaDecl.cpp

Log Message:

-----------

[clang] Fix sanitizer bot failure after 14ca8d4 (#73928)

Initialize field so there is no use-of-uninitialized-value warning.

Commit: 8b25381bb6221dcfd2295aa2fd819f5b97704ca1

https://github.com/llvm/llvm-project/commit/8b25381bb6221dcfd2295aa2fd819f5b97704ca1

Author: Guillaume Chatelet <gchatelet at google.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M libc/src/__support/CPP/CMakeLists.txt

M libc/src/__support/CPP/limits.h

M utils/bazel/llvm-project-overlay/libc/BUILD.bazel

Log Message:

-----------

[libc] Add the digits property to numeric_limits (#73926)

Commit: 2ec0283c0405535594a46ea4244b09e63a797f0b

https://github.com/llvm/llvm-project/commit/2ec0283c0405535594a46ea4244b09e63a797f0b

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/IR/BasicBlock.h

M llvm/include/llvm/IR/DebugProgramInstruction.h

M llvm/include/llvm/IR/Instruction.h

M llvm/lib/IR/BasicBlock.cpp

M llvm/lib/IR/DebugProgramInstruction.cpp

M llvm/lib/IR/Instruction.cpp

M llvm/unittests/IR/BasicBlockDbgInfoTest.cpp

Log Message:

-----------

[DebugInfo][RemoveDIs] Emulate inserting insts in dbg.value sequences (#73350)

Here's a problem for the RemoveDIs project to make debug-info not be

stored in instructions -- in the following sequence:

dbg.value(foo

%bar = add i32 ...

dbg.value(baz

It's possible for rare passes (only CodeGenPrepare) to remove the add

instruction, and then re-insert it back in the same place. When

debug-info is stored in instructions and there's a total order on "when"

things happen this is easy, but by moving that information out of the

instruction stream we start having to do manual maintenance.

This patch adds some utilities for re-inserting an instruction into a

sequence of DPValue objects. Someday we hope to design this away, but

for now it's necessary to support all the things you can do with

dbg.values. The two unit tests show how DPValues get shuffled around

using the relevant function calls. A follow-up patch adds

instrumentation to CodeGenPrepare.

Commit: b703bd821d011011431c3a961e816b8fc33912da

https://github.com/llvm/llvm-project/commit/b703bd821d011011431c3a961e816b8fc33912da

Author: Guillaume Chatelet <gchatelet at google.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M libc/src/__support/CPP/CMakeLists.txt

M libc/src/__support/CPP/bit.h

M libc/test/src/__support/CPP/CMakeLists.txt

A libc/test/src/__support/CPP/bit_test.cpp

M utils/bazel/llvm-project-overlay/libc/BUILD.bazel

M utils/bazel/llvm-project-overlay/libc/test/src/__support/CPP/BUILD.bazel

Log Message:

-----------

[libc] Add more functions in CPP/bit.h (#73814)

Once this is submitted we can remove `include/__support/bit.h` that

duplicates some of this functionality.

Commit: b8a5a015d12c698a3254898c94d0adffe0724fa8

https://github.com/llvm/llvm-project/commit/b8a5a015d12c698a3254898c94d0adffe0724fa8

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineSimplifyDemanded.cpp

Log Message:

-----------

[InstCombine] Use pointer alignment in SimplifyDemandedBits

For parity with computeKnownBits(). This came up when adding a

consistency assertion.

Commit: 5ba5211a477f0d513eaed2b35e04239f005a30bd

https://github.com/llvm/llvm-project/commit/5ba5211a477f0d513eaed2b35e04239f005a30bd

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/IR/Instructions.h

M llvm/include/llvm/Transforms/Utils/LoopUtils.h

M llvm/lib/IR/Instructions.cpp

M llvm/lib/Transforms/Scalar/LICM.cpp

M llvm/test/DebugInfo/X86/licm-undef-dbg-value.ll

A llvm/test/Transforms/LICM/dbg-value-sink.ll

M llvm/test/Transforms/LICM/debug-value.ll

M llvm/test/Transforms/LICM/hoist-debuginvariant.ll

Log Message:

-----------

[DebugInfo][RemoveDIs] Have LICM insert at iterator positions (#73671)

Because we're storing some extra debug-info information in the iterator

class, we need to insert new LICM-created stores using such iterators.

Switch LICM to storing iterators instead of pointers when it promotes

variables in loops, add a test for the desired behaviour, and enable

RemoveDIs instrumentation on a variety of other LICM tests for good

measure.

(This would appear to be the only pass in LLVM that needs to store

iterators on the heap).

Commit: 1566380e6b47d7876c0f3eaa105097063dbe7cc8

https://github.com/llvm/llvm-project/commit/1566380e6b47d7876c0f3eaa105097063dbe7cc8

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/Analysis/ValueTracking.h

M llvm/lib/Analysis/ValueTracking.cpp

M llvm/lib/Transforms/InstCombine/InstCombineSimplifyDemanded.cpp

Log Message:

-----------

[ValueTracking] Switch analyzeKnownBitsFromAndXorOr() to use SimplifyQuery (NFC)

It already used it internally, make the public API use it as well.

Commit: 3f6a8e9b18154accc78e620b843b3721c23703b1

https://github.com/llvm/llvm-project/commit/3f6a8e9b18154accc78e620b843b3721c23703b1

Author: Antonio Frighetto <me at antoniofrighetto.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/Transforms/InstCombine/add3.ll

M llvm/test/Transforms/InstCombine/addnegneg.ll

Log Message:

-----------

[InstCombine] Switch to use FileCheck as UTC was favoured (NFC)

FileCheck was previously missing while moving to UTC, as part of

regenerating other tests within InstCombine.

Commit: 062058ef36c3a5a41f5c2ad2fd1a53f7a099e956

https://github.com/llvm/llvm-project/commit/062058ef36c3a5a41f5c2ad2fd1a53f7a099e956

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineSimplifyDemanded.cpp

Log Message:

-----------

[InstCombine] Use analyzeKnownBitsFromAndXorOr() in multi-use demanded bits

We were using this helper in single-use demanded bits but not

multi-use demanded bits.

This fixes an assertion failure when asserting consistency between

computeKnownBits() and SimplifyDemandedBits().

Commit: 2031e7226cc5318c547c6d3f62ac62d369d0e723

https://github.com/llvm/llvm-project/commit/2031e7226cc5318c547c6d3f62ac62d369d0e723

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineSimplifyDemanded.cpp

Log Message:

-----------

[InstCombine] Require non-demanded known bits to be accurate (NFC)

In practice this is already true, and having this as an explicit

guarantee is useful for #72912. I don't think there is any good

reason why we would want to produce incorrect KnownBits results

for non-demanded bits.

Commit: c44dca15a4297eef3b9319a5e24f85267a099642

https://github.com/llvm/llvm-project/commit/c44dca15a4297eef3b9319a5e24f85267a099642

Author: Matt Arsenault <Matthew.Arsenault at amd.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/CodeGen/MIRParser/MIParser.cpp

M llvm/lib/CodeGen/MachineInstr.cpp

M llvm/lib/CodeGen/MachineVerifier.cpp

M llvm/lib/Target/MSP430/MSP430RegisterInfo.cpp

R llvm/test/CodeGen/MIR/AMDGPU/extra-imm-operand.mir

R llvm/test/CodeGen/MIR/AMDGPU/extra-reg-operand.mir

A llvm/test/MachineVerifier/verify-implicit-def.mir

Log Message:

-----------

MachineVerifier: Reject extra non-register operands on instructions (#73758)

We were allowing extra immediate arguments, and only bothering to check

if registers were implicit or not.

Also consolidate extra operand checks in verifier, to make this

testable. We had 3 different places checking if you were trying to build

an instruction with more operands than allowed by the definition. We had

an assertion in addOperand, a direct check in the MIRParser to avoid the

assertion, and the machine verifier checks. Remove the assert and parser

check so the verifier can provide a consistent verification experience,

which will also handle instructions modified in place.

Commit: 29a0f3ec2b47630ce229953fe7250e741b6c10b6

https://github.com/llvm/llvm-project/commit/29a0f3ec2b47630ce229953fe7250e741b6c10b6

Author: leecheechen <chenli at loongson.cn>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/add.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/ashr.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/fadd.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/fdiv.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/fmul.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/fsub.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/lshr.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/mul.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/sdiv.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/shl.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/sub.ll

A llvm/test/CodeGen/LoongArch/lsx/ir-instruction/udiv.ll

Log Message:

-----------

[LoongArch] Add some binary IR instructions testcases for LSX (#73929)

The IR instructions include:

- Binary Operations: add fadd sub fsub mul fmul udiv sdiv fdiv

- Bitwise Binary Operations: shl lshr ashr

Commit: cd02e4b8128e6379f1b317132f605787074c8850

https://github.com/llvm/llvm-project/commit/cd02e4b8128e6379f1b317132f605787074c8850

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/IR/DIBuilder.cpp

Log Message:

-----------

[DebugInfo] Set all dbg.value intrinsics to be tail-calls (#73661)

This change has no meaningful effect on the compiler, although it has a

functional effect of dbg.value intrinsics being printed differently. The

tail-call flag is meaningless for debug-intrinsics and doesn't serve a

purpose, it's just extra baggage that dbg.values are built on top of.

Some facilities create debug-intrinsics with the flag, others don't.

However, the RemoveDIs project to represent debug-info without

intrinsics doesn't have a corresponding flag, which can cause spurious

test differences.

Specifically: we can convert a dbg.value to a DPValue, run an

optimisation pass, then convert the DPValue back to dbg.value form.

Right now, we always set the "tail" flag when converting it back. This

causes the auto-update-tests script to fail sometimes because in one

mode (dbg.value) intrinsics might not have a tail flag, but in the other

they do have a tail flag. Consistently picking one or the other in the

conversion routine doesn't help, because the rest of LLVM is

inconsistent about it anyway.

Thus: whenever we make a dbg.value intrinsic, create it as a tail call,

so that we get consistent output behaviours no matter which debug-info

mode we're in, DPValue or dbg.value. No tests fail as a result of this

patch because the extra 'tail' generated in numerous tests is

automatically ignored by FileCheck as being leading-rubbish before the

CHECK match.

Commit: 10b44fb6a38fd68b78933b89c3b6d8cff20485a8

https://github.com/llvm/llvm-project/commit/10b44fb6a38fd68b78933b89c3b6d8cff20485a8

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombineSimplifyDemanded.cpp

Log Message:

-----------

[InstCombine] Add KnownBits consistency assertion behind option (NFC)

I'm occasionally using this to find cases where computeKnownBits()

and SimplifyDemandedBits() went out of sync.

This option is not enabled by default (even under EXPENSIVE_CHECKS)

because it has a number of known failures in our tests. The reason

for this failures is that computeKnownBits() performs recursive

queries using the original context instruction, while

SimplifyDemandedBits() uses the current instruction. This is

something we can improve, but using the original context wouldn't

always be safe in this context (when non-speculatable instructions

are involved).

Commit: 1c2a0768de7a670161b90f9eac8bbe484ad017a6

https://github.com/llvm/llvm-project/commit/1c2a0768de7a670161b90f9eac8bbe484ad017a6

Author: Adam Paszke <apaszke at google.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/lib/ExecutionEngine/CudaRuntimeWrappers.cpp

Log Message:

-----------

[MLIR][CUDA] Update export macros in CudaRuntimeWrappers (#73932)

This fixes a few issues present in the current version:

1) The macro doesn't enforce the default visibility on exported

functions, causing compilation to fail when using

`-fvisibility=hidden`

2) Not all functions are exported

3) Sometimes the macro ended up weirdly interleaved with `extern "C"`

declarations

Commit: 78237b70c873eb58877d91782a7f8eeb3fdf4901

https://github.com/llvm/llvm-project/commit/78237b70c873eb58877d91782a7f8eeb3fdf4901

Author: Lucas Duarte Prates <lucas.prates at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/AArch64/AArch64SVEInstrInfo.td

M llvm/test/MC/AArch64/SVE/armv9.5a-cpa.s

Log Message:

-----------

[AArch64] Fix predicates for FEAT_CPA's SVE-specific instructions (#73923)

Following up on #73777, this fixes the predicate for the SVE-specific

FEAT_CPA instructions to require SVE instead of SVE or SME. These

instructions should not be availabe if only SME is enabled.

Commit: 6677f029b2d177aaeea94df0f8ba67e760e43d4b

https://github.com/llvm/llvm-project/commit/6677f029b2d177aaeea94df0f8ba67e760e43d4b

Author: Hui <hui.xie0621 at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M libcxx/test/libcxx/atomics/atomics.types.generic/atomics.types.float/lockfree.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/assign.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/compare_exchange_strong.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/compare_exchange_weak.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/ctor.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/exchange.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/fetch_add.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/fetch_sub.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/load.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/lockfree.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/notify_all.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/notify_one.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.float.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.minus_equals.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/operator.plus_equals.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/store.pass.cpp

M libcxx/test/std/atomics/atomics.types.generic/atomics.types.float/wait.pass.cpp

M libcxx/test/std/atomics/atomics.types.operations/atomics.types.operations.wait/atomic_notify_all.pass.cpp

M libcxx/utils/libcxx/test/features.py

Log Message:

-----------

[libc++] Workaround linker errors in floating-point atomic tests (#73398)

We now add -latomic whenever we detect that it's supported on the platform,

and we mark the tests as UNSUPPORTED on platforms where non-lockfree

atomics are not supported.

Commit: 402591a4147ceaee48afc8712d0c61f6402df67b

https://github.com/llvm/llvm-project/commit/402591a4147ceaee48afc8712d0c61f6402df67b

Author: frgossen <frgossen at google.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M utils/bazel/llvm-project-overlay/mlir/BUILD.bazel

Log Message:

-----------

Fix bazel build (#73942)

Commit: 99d485917ae5f10629cb9d7ca96b7cd6773ac35f

https://github.com/llvm/llvm-project/commit/99d485917ae5f10629cb9d7ca96b7cd6773ac35f

Author: David Spickett <david.spickett at linaro.org>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/AArch64/AArch64ExpandPseudoInsts.cpp

A llvm/test/CodeGen/AArch64/blr-bti-preserves-regmask.mir

M llvm/test/CodeGen/AArch64/kcfi-bti.ll

Log Message:

-----------

[llvm][AArch64] Preserve regmask when expanding the BLR_BTI pseudo instruction (#73927)

Fixes #73787

Not doing so lead to us making use of a register after the call, which

has been clobbered by the call.

Added an MIR test that runs only the pseudo expansion pass.

Commit: a4e1aa256b14d74da47fdfeb245930a520f5fd64

https://github.com/llvm/llvm-project/commit/a4e1aa256b14d74da47fdfeb245930a520f5fd64

Author: Shengchen Kan <shengchen.kan at intel.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/include/llvm/Support/X86FoldTablesUtils.h

M llvm/lib/Target/X86/X86InstrFoldTables.cpp

M llvm/test/CodeGen/X86/dpbusd_const.ll

M llvm/test/TableGen/x86-fold-tables.inc

M llvm/utils/TableGen/X86FoldTablesEmitter.cpp

Log Message:

-----------

[X86][tablgen] Auto-gen broadcast tables (#73654)

1. Add TB_BCAST_SH for FP16

2. Auto-gen 4 broadcast tables BroadcastTable[1-4]

issue: https://github.com/llvm/llvm-project/issues/66360

Commit: 4c338f80c40b85a704bac455d0487ccaf2b26fb1

https://github.com/llvm/llvm-project/commit/4c338f80c40b85a704bac455d0487ccaf2b26fb1

Author: Dominik Wójt <dominik.wojt at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M libcxx/include/__locale

Log Message:

-----------

[libc++] picolibc: avoid warning in __locale (#73937)

Commit: 1f88e62db40950d48ee83ea31281689c54016709

https://github.com/llvm/llvm-project/commit/1f88e62db40950d48ee83ea31281689c54016709

Author: Alexey Bataev <a.bataev at outlook.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/Vectorize/SLPVectorizer.cpp

M llvm/test/Transforms/SLPVectorizer/X86/minbitwidth-transformed-operand.ll

Log Message:

-----------

[SLP]Fix/improve minbitwidth mapping to use TreeEntry as a key.

Currently, MinBWs map uses Value* as a key and stores mapping for each

value to be demoted. It make is it hard to get the actual MinBWs value

for the buildvector scalars(constants), since same constant might be

used in different nodes with the different MinBWs values/decisions.

Also, it consumes extra memory for the vectorized values/instructions

from the same nodes.

Better to map actual nodes. It fixes the bitwidth data fetching for

buildvector scalars and improves memory consumption/analysis time for

other instructions.

Commit: 5234fe31547737f4fc9d312946cb647968734da1

https://github.com/llvm/llvm-project/commit/5234fe31547737f4fc9d312946cb647968734da1

Author: Sam Tebbs <samuel.tebbs at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/include/clang/Basic/DiagnosticSemaKinds.td

M clang/lib/Sema/SemaChecking.cpp

A clang/test/Sema/aarch64-incompat-sm-builtin-calls.c

Log Message:

-----------

[AArch64] Warn when calling a NEON builtin in a streaming function (#73672)

This patch introduces a warning that is emitted when a Neon builtin is

called from a streaming function, as that situation is not supported.

Uses work by Kerry McLaughlin.

Commit: ba523106579fd26d52e16c1a6f4eeb839d84351f

https://github.com/llvm/llvm-project/commit/ba523106579fd26d52e16c1a6f4eeb839d84351f

Author: Alexey Bataev <5361294+alexey-bataev at users.noreply.github.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/Vectorize/SLPVectorizer.cpp

Log Message:

-----------

[SLP][NFC] Unify code for cost estimation/codegen for buildvector, NFC. (#73182)

This just moves towards reusing same function for both cost

estimation/codegen for buildvector.

Commit: b8bbd5fe6f6371f549e0aedf726fa47e7dd3bbf6

https://github.com/llvm/llvm-project/commit/b8bbd5fe6f6371f549e0aedf726fa47e7dd3bbf6

Author: Simon Pilgrim <llvm-dev at redking.me.uk>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/X86/X86InstrFoldTables.cpp

Log Message:

-----------

[X86] X86InstrFoldTables.cpp - add Op4 Broadcast Fold/Unfold table entries

Prep work for #73509 (missed in #73654)

Commit: b7af286a4e3e2e5464b95ddfca0ed793bb4aa8b9

https://github.com/llvm/llvm-project/commit/b7af286a4e3e2e5464b95ddfca0ed793bb4aa8b9

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/Transforms/InstCombine/phi.ll

Log Message:

-----------

[InstCombine] Add test for "or disjoint" miscompile (NFC)

Commit: d8bc5465330474b80c02ca37e76a9a51245f1d79

https://github.com/llvm/llvm-project/commit/d8bc5465330474b80c02ca37e76a9a51245f1d79

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstCombinePHI.cpp

M llvm/test/Transforms/InstCombine/phi.ll

Log Message:

-----------

[InstCombine] Fix phi or icmp fold with disjoint flag

We're changing the operand of the or here, such that the disjoint

flag may no longer hold. Clear it.

Commit: 73d9f5fda6648a9c75a265524da29bac061fb155

https://github.com/llvm/llvm-project/commit/73d9f5fda6648a9c75a265524da29bac061fb155

Author: Piotr Sobczak <piotr.sobczak at amd.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/CodeGen/AMDGPU/regpressure_printer.mir

Log Message:

-----------

[AMDGPU] Add test for GCNRegPressure tracker bug (#73786)

Add a test to document an existing problem in GCNRegPressure tracker.

The upward tracker does not count the registers used (16 of them) in

movrel instruction (for example V_INDIRECT_REG_WRITE_MOVREL_B32_V16).

The downward tracker counts the registers but reports a mismatch:

%0:L0000000000000C00 isn't found in LIS reported set

Commit: 3ef98bcd46f22d1d25f9f83f5742209f87d399d0

https://github.com/llvm/llvm-project/commit/3ef98bcd46f22d1d25f9f83f5742209f87d399d0

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/CodeGen/CodeGenPrepare.cpp

M llvm/lib/IR/BasicBlock.cpp

M llvm/test/DebugInfo/X86/codegenprep-addrsink.ll

A llvm/test/DebugInfo/X86/codegenprepare-rollback.ll

M llvm/test/Transforms/CodeGenPrepare/X86/catchpad-phi-cast.ll

M llvm/test/Transforms/CodeGenPrepare/X86/cttz-ctlz.ll

M llvm/test/Transforms/CodeGenPrepare/X86/select.ll

M llvm/test/Transforms/CodeGenPrepare/sink-shift-and-trunc.ll

Log Message:

-----------

[DebugInfo][RemoveDIs] Support maintaining DPValues in CodeGenPrepare (#73660)

CodeGenPrepare needs to support the maintenence of DPValues, the

non-instruction replacement for dbg.value intrinsics. This means there are

a few functions we need to duplicate or replicate the functionality of:

* fixupDbgValue for setting users of sunk addr GEPs,

* The remains of placeDbgValues needs a DPValue implementation for sinking

* Rollback of RAUWs needs to update DPValues

* Rollback of instruction removal needs supporting (see github #73350)

* A few places where we have to use iterators rather than instructions.

There are three places where we have to use the setHeadBit call on

iterators to indicate which portion of debug-info records we're about to

splice around. This is because CodeGenPrepare, unlike other optimisation

passes, is very much concerned with which block an operation occurs in and

where in the block instructions are because it's preparing things to be in

a format that's good for SelectionDAG.

There isn't a large amount of test coverage for debuginfo behaviours in

this pass, hence I've added some more.

Commit: 0ef013c823e108d477ab749f3187d939e10f8333

https://github.com/llvm/llvm-project/commit/0ef013c823e108d477ab749f3187d939e10f8333

Author: Dinar Temirbulatov <Dinar.Temirbulatov at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/include/clang/Basic/arm_sve.td

A clang/test/CodeGen/aarch64-sme2-intrinsics/acle_sme2_vector_selx2.c

A clang/test/CodeGen/aarch64-sme2-intrinsics/acle_sme2_vector_selx4.c

Log Message:

-----------

[AArch64][SME2] Add multi-vector SEL (x2, x4) ACLE builtins & intrinsics (#73188)

Add multi-vector SEL (x2, x4) ACLE builtins & intrinsics

Patch by: David Sherwood <david.sherwood at arm.com>

Commit: ff5e536b5e3b59fbc40df0e24494c6ce7417e2ea

https://github.com/llvm/llvm-project/commit/ff5e536b5e3b59fbc40df0e24494c6ce7417e2ea

Author: Philip Reames <preames at rivosinc.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/RISCV/RISCVISelLowering.cpp

M llvm/test/CodeGen/RISCV/rvv/concat-vector-insert-elt.ll

M llvm/test/CodeGen/RISCV/rvv/fixed-vectors-buildvec-of-binop.ll

Log Message:

-----------

[RISCV] Add combines to form binop from tail insert idioms (#72675)

This patch contains two related combines:

1) If we have an scalar vector insert into the result of a

concat_vector,

sink the insert into the operand of the concat.

2) If we have a insert of a scalar binop into a vector binop of the

same opcode and the RHS of both are constant, perform the insert

and then the binop.

The common theme to both is pushing inserts closer to the sources of the

computation graph. The goal is to enable forming vector bin ops from

inserts of scalar binops at the end of another vector.

For RISCV specifically, the concat_vector transform will push inserts to

smaller vectors. This will have the effect of reducing lmul for the

vslides, and usually doesn't require an additional vsetvli since

the source vectors are already working in the narrower VL. I tried

that one as a target independent combine first, and it doesn't appear

profitable on all targets.

This is only one approach to the problem. Another idea would be to

aggressively form build_vectors and subvector inserts from the

individual scalar inserts, and then have a transform which sunk a

subvector_insert down through the concat. The advantage of the alternate

approach is that we expose parallelism in the insert sequence, even if

the source vector isn't a concat_vector. If reviewers are okay with it,

I'd like to start with this approach, and then explore that direction in

a follow up patch.

Commit: 8eb705321ed20232aa13e85e07f22b44f19e82b4

https://github.com/llvm/llvm-project/commit/8eb705321ed20232aa13e85e07f22b44f19e82b4

Author: Lucas Prates <lucas.prates at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/MC/AArch64/armv9.5a-cpa.s

Log Message:

-----------

[AArch64][MC] Fix run line in Armv9.5-A's FEAT_CPA test

Commit: c89553ae829e05ac830eff80e69775704a8ba040

https://github.com/llvm/llvm-project/commit/c89553ae829e05ac830eff80e69775704a8ba040

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/Transforms/InstSimplify/select.ll

Log Message:

-----------

[InstSimplify] Add test for or disjoint miscompile (NFC)

Commit: 07c18a05e2cb80e87b0c681c147a253565064f3e

https://github.com/llvm/llvm-project/commit/07c18a05e2cb80e87b0c681c147a253565064f3e

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Analysis/InstructionSimplify.cpp

M llvm/test/Transforms/InstSimplify/select.ll

Log Message:

-----------

[InstSimplify] Fix select bit test miscompile with disjoint

The select condition ensures the disjointness here. The transform

is not valid without dropping the flag, which InstSimplify can't

do.

Commit: 1d05b21e035f579af2f96b4a61847d2c9f358ac2

https://github.com/llvm/llvm-project/commit/1d05b21e035f579af2f96b4a61847d2c9f358ac2

Author: Aaron Ballman <aaron at aaronballman.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/test/Preprocessor/suggest-typoed-directive.c

Log Message:

-----------

Add test coverage for -Wunknown-directives; NFC

While working on #embed, I noticed that the PR accidentally broke the

warning group but no tests failed as a result. This is adding the

missing test coverage.

Commit: e4f951e4eef6128a2e9d8fc103e4402315484d65

https://github.com/llvm/llvm-project/commit/e4f951e4eef6128a2e9d8fc103e4402315484d65

Author: Louis Dionne <ldionne.2 at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M clang/lib/Driver/ToolChains/Darwin.cpp

Log Message:

-----------

[clang][NFC] Fix typo in comment about Mac Catalyst

Commit: 3f505cd58776fca59f4f2eb456b169fa5da09317

https://github.com/llvm/llvm-project/commit/3f505cd58776fca59f4f2eb456b169fa5da09317

Author: Samira Bazuzi <bazuzi at users.noreply.github.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M libc/src/__support/CPP/bitset.h

Log Message:

-----------

[libc] Mark operator== const to avoid ambiguity in C++20. (#73954)

C++20 will automatically generate an operator== with reversed operand

order, which is ambiguous with the written operator== when one argument

is marked const and the other isn't.

This operator currently triggers -Wambiguous-reversed-operator at

several usage sites in libc/test/src/__support/CPP/bitset_test.cpp,

starting with line 153.

Commit: ca5a01d8e473eb4c3e6a3e2061875f7ca958d748

https://github.com/llvm/llvm-project/commit/ca5a01d8e473eb4c3e6a3e2061875f7ca958d748

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/test/Transforms/InstSimplify/freeze-noundef.ll

Log Message:

-----------

[InstSimplify] Add test for incorrect freeze of or disjoint (NFC)

Commit: ea602cb80678fbf5f52bbbda142437164b2a3407

https://github.com/llvm/llvm-project/commit/ea602cb80678fbf5f52bbbda142437164b2a3407

Author: Nikita Popov <npopov at redhat.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/IR/Operator.cpp

M llvm/test/Transforms/InstSimplify/freeze-noundef.ll

Log Message:

-----------

[IR] Support or disjoint in hasPoisonGeneratingFlags()

This fixed incorrect removal of freeze instructions.

Commit: 442490315685944b71037bccc410048fb3612060

https://github.com/llvm/llvm-project/commit/442490315685944b71037bccc410048fb3612060

Author: Jeremy Morse <jeremy.morse at sony.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Transforms/InstCombine/InstructionCombining.cpp

M llvm/lib/Transforms/Scalar/JumpThreading.cpp

M llvm/lib/Transforms/Utils/PromoteMemoryToRegister.cpp

M llvm/test/DebugInfo/Generic/mem2reg-promote-alloca-1.ll

M llvm/test/DebugInfo/Generic/mem2reg-promote-alloca-2.ll

M llvm/test/DebugInfo/Generic/mem2reg-promote-alloca-3.ll

M llvm/test/DebugInfo/Generic/volatile-alloca.ll

M llvm/test/DebugInfo/X86/mem2reg_fp80.ll

M llvm/test/Transforms/InstCombine/cast-set-preserve-signed-dbg-val.ll

M llvm/test/Transforms/InstCombine/consecutive-fences.ll

M llvm/test/Transforms/InstCombine/dbg-scalable-store-fixed-frag.ll

M llvm/test/Transforms/InstCombine/debuginfo-dce2.ll

M llvm/test/Transforms/InstCombine/debuginfo-skip.ll

M llvm/test/Transforms/InstCombine/debuginfo.ll

M llvm/test/Transforms/InstCombine/debuginfo_add.ll

M llvm/test/Transforms/InstCombine/erase-dbg-values-at-dead-alloc-site.ll

M llvm/test/Transforms/InstCombine/lower-dbg-declare.ll

M llvm/test/Transforms/InstCombine/pr43893.ll

M llvm/test/Transforms/InstCombine/sink-instruction-introduces-unnecessary-poison-value.ll

M llvm/test/Transforms/InstCombine/stacksave-debuginfo.ll

M llvm/test/Transforms/InstCombine/unavailable-debug.ll

Log Message:

-----------

[DebugInfo][RemoveDIs] Handle DPValues at remaining dbg.value using sites (#73788)

This patch updates the last few places in LLVM using findDbgValues that

don't also collect and handle DPValue objects. This largely involves

instcombine and mem2reg changes, and are largely mechanical, calling

existing utilities on collections of DPValues instead of just

DbgValuesInsts.

A variety of tests have had RemoveDIs RUN lines added to them to cover

these behaviours. We have some technical debt of the instcombine sinking

code for DPValues not being implemented yet, so I've left FIXME stubs

indicating that we intend to cover tests with RemoveDIs but haven't yet.

Commit: a51196ec6ed784eae9ca4d0feca3a582c8dfefd5

https://github.com/llvm/llvm-project/commit/a51196ec6ed784eae9ca4d0feca3a582c8dfefd5

Author: Youngsuk Kim <youngsuk.kim at hpe.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/tools/llvm-reduce/deltas/ReduceOpcodes.cpp

Log Message:

-----------

[llvm-reduce] Remove unreachable branch (NFC)

Remove stale branch which is unreachable with opaque pointers.

Commit: a383817b7e24d948dd5e342e8df8d12d0f15d536

https://github.com/llvm/llvm-project/commit/a383817b7e24d948dd5e342e8df8d12d0f15d536

Author: Andrzej Warzyński <andrzej.warzynski at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M mlir/lib/Dialect/Vector/Transforms/LowerVectorGather.cpp

M mlir/test/Dialect/Vector/vector-gather-lowering.mlir

Log Message:

-----------

[mlir][Vector] Add a rewrite pattern for gather over a strided memref (#72991)

This patch adds a rewrite pattern for `vector.gather` over a strided

memref like the following:

```mlir

%subview = memref.subview %arg0[0, 0] [100, 1] [1, 1] :

memref<100x3xf32> to memref<100xf32, strided<[3]>>

%gather = vector.gather %subview[%c0] [%idxs], %cst_0, %cst :

memref<100xf32, strided<[3]>>, vector<4xindex>, vector<4xi1>, vector<4xf32>

into vector<4xf32>

```

After the pattern added in this patch:

```mlir

%collapse_shape = memref.collapse_shape %arg0 [[0, 1]] :

memref<100x3xf32> into memref<300xf32>

%1 = arith.muli %arg3, %cst : vector<4xindex>

%gather = vector.gather %collapse_shape[%c0] [%1], %cst_1, %cst_0 :

memref<300xf32>, vector<4xindex>, vector<4xi1>, vector<4xf32>

into vector<4xf32>

```

Fixes https://github.com/openxla/iree/issues/15364.

Commit: 6976dac09db6dab3ef9eb68f1d19b70aa2847773

https://github.com/llvm/llvm-project/commit/6976dac09db6dab3ef9eb68f1d19b70aa2847773

Author: Michael Maitland <michaeltmaitland at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/RISCV/GISel/RISCVInstructionSelector.cpp

M llvm/lib/Target/RISCV/GISel/RISCVRegisterBankInfo.cpp

M llvm/lib/Target/RISCV/GISel/RISCVRegisterBankInfo.h

A llvm/test/CodeGen/RISCV/GlobalISel/instruction-select/implicit-def-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/instruction-select/implicit-def-rv64.mir

A llvm/test/CodeGen/RISCV/GlobalISel/regbankselect/implicit-def-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/regbankselect/implicit-def-rv64.mir

Log Message:

-----------

[RISCV][GISEL] regbankselect and instruction-select for G_IMPLICIT_DEF (#73060)

This is similar to the selection of G_IMPLICIT_DEF in AArch64.

Regbankselect may need to be improved in a future patch.

Commit: dbb9043dea238fa4e5b6a9a7fef99623b543493e

https://github.com/llvm/llvm-project/commit/dbb9043dea238fa4e5b6a9a7fef99623b543493e

Author: Michael Maitland <michaeltmaitland at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/RISCV/GISel/RISCVInstructionSelector.cpp

M llvm/lib/Target/RISCV/GISel/RISCVLegalizerInfo.cpp

M llvm/lib/Target/RISCV/GISel/RISCVRegisterBankInfo.cpp

A llvm/test/CodeGen/RISCV/GlobalISel/instruction-select/merge-unmerge-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/irtranslator/bitcast-between-f64-and-i64.ll

A llvm/test/CodeGen/RISCV/GlobalISel/legalizer/merge-unmerge-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/legalizer/merge-unmerge-rv32d.mir

A llvm/test/CodeGen/RISCV/GlobalISel/legalizer/merge-unmerge-rv64.mir

A llvm/test/CodeGen/RISCV/GlobalISel/regbankselect/merge-unmerge-rv32.mir

Log Message:

-----------

[RISCV][GISEL] legalize, regbankselect, and instruction-select for G_… (#73061)

…[UN]MERGE_VALUES

When MERGE or UNMERGE s64 on a subtarget that is non-64bit, it must have

the D extension and use FPR in order to be legal.

All other instances of MERGE and UNMERGE that can be made legal should

be narrowed, widend, or replaced by the combiner.

Commit: a6f72785951b36c0c02227bf4eac4ea733fa6694

https://github.com/llvm/llvm-project/commit/a6f72785951b36c0c02227bf4eac4ea733fa6694

Author: Michael Maitland <michaeltmaitland at gmail.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/RISCV/GISel/RISCVInstructionSelector.cpp

M llvm/lib/Target/RISCV/GISel/RISCVLegalizerInfo.cpp

A llvm/test/CodeGen/RISCV/GlobalISel/instruction-select/ptrmask-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/instruction-select/ptrmask-rv64.mir

A llvm/test/CodeGen/RISCV/GlobalISel/legalizer/legalize-ptrmask-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/legalizer/legalize-ptrmask-rv64.mir

A llvm/test/CodeGen/RISCV/GlobalISel/regbankselect/ptrmask-rv32.mir

A llvm/test/CodeGen/RISCV/GlobalISel/regbankselect/ptrmask-rv64.mir

Log Message:

-----------

[RISCV][GISEL] legalize, regbankselect, and instruction-select G_PTRMASK (#73062)

This is done in instruction-select instead of in legalization for the

sake of alias analysis.

Commit: 4d8012259846274c6122b3befdff32d4c3010f7c

https://github.com/llvm/llvm-project/commit/4d8012259846274c6122b3befdff32d4c3010f7c

Author: David Green <david.green at arm.com>

Date: 2023-11-30 (Thu, 30 Nov 2023)

Changed paths:

M llvm/lib/Target/AArch64/AArch64FrameLowering.cpp